www.FirstRanker.com

Enrolment. FirstRanker.com

## GUJARAT TECHNOLOGICAL UNIVERSITY

|                                        |              | BE - SEMESTER- III (New) EXAMINATION – WINTER 2019                                               |       |

|----------------------------------------|--------------|--------------------------------------------------------------------------------------------------|-------|

| Subject Code: 3131704 Date: 26/11/2    |              |                                                                                                  |       |

| Subje                                  | ect Na       | me: Digital Electronics                                                                          |       |

| Time: 02:30 PM TO 05:00 PM Total Marks |              |                                                                                                  | 70    |

| Instrue                                |              |                                                                                                  |       |

|                                        |              | tempt all questions.                                                                             |       |

|                                        |              | ake suitable assumptions wherever necessary.<br>gures to the right indicate full marks.          |       |

|                                        | <b>з.</b> гц | gures to the right mulcate fun marks.                                                            | MARKS |

| Q.1                                    | (a)          | Give the comparison of 1's and 2's complements.                                                  | 03    |

| <b>V</b> .1                            | (b)          | Explain De Morgan's theorem with suitable example.                                               | 04    |

|                                        | (c)          | Explain the commutative law, associative law, and distributive law in                            | 07    |

|                                        |              | Boolean algebra with example                                                                     |       |

| Q.2                                    | (a)          | Convert $(163.875)_{10}$ to binary.                                                              | 03    |

|                                        | <b>(b)</b>   | Design Full Adder using two Half Adder and one two input OR gate.                                | 04    |

|                                        | (c)          | Implement the following function with 8:1 multiplexer:                                           | 07    |

|                                        |              | $F(A, B, C, D) = \sum (0, 1, 3, 4, 8, 9, 15)$ <b>OR</b>                                          |       |

|                                        | (c)          | Explain the working of 4:1 multiplexer.                                                          | 07    |

|                                        | (0)          | Explain the working of 1.1 metuplexel.                                                           | 07    |

| Q.3                                    | <b>(a)</b>   | What do you mean by universal gates? Implement NOT, AND, OR with                                 | 03    |

|                                        |              | any one universal gate.                                                                          |       |

|                                        | ( <b>b</b> ) | Implement 4 bit Shift Register for 1010 binary pattern.                                          | 04    |

|                                        | ( <b>c</b> ) | A combinational circuit is defined by functions:<br>$F_1(A, B, C) = \sum_{i=1}^{n} (2, 5, C, T)$ | 07    |

|                                        |              | F1 (A,B,C) = $\sum m(3, 5, 6, 7)$<br>F2 (A,B,C) = $\sum m(0, 2, 4, 7)$                           |       |

|                                        |              | Implement the circuit with PLA having three inputs, four product terms                           |       |

|                                        |              | and two outputs.                                                                                 |       |

|                                        |              | OR                                                                                               |       |

| Q.3                                    | <b>(a)</b>   | Explain the operation of master slave J-K flip flop.                                             | 03    |

|                                        | <b>(b)</b>   | Explain gray code in detail.                                                                     | 04    |

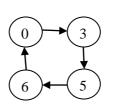

(c) Design a type T counter for given state diagram 07

| Q.4 | (a)        | Describe Fan In, Noise Margin and Propagation Delay parameters for | 03 |

|-----|------------|--------------------------------------------------------------------|----|

|     |            | digital IC.                                                        |    |

|     | <b>(b)</b> | xplain ROM with block diagram. Give classification of ROM.         | 04 |

|     | (c)        | Design 3 to 8 line decoder with neat sketch and truth table.       | 07 |

|     | , í        | OR                                                                 |    |

| Q.4 | <b>(a)</b> | Simplify Boolean function $F = A'B'C'+B'CD'+A'BCD'+AB'C'$          | 03 |

|     |            | using K map.                                                       |    |

|     | <b>(b)</b> | Explain TTL gate with Totem pole output.                           | 04 |

www.FirstRanker.com

|     | (c) -      | explain 4 bit magnitude instruction ecessary Boole PirstrasiRer.co                                                                    | om V/ |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------|-------|

| Q.5 | <b>(a)</b> | Explain D flip-flop.                                                                                                                  | 03    |

|     | <b>(b)</b> | Explain arithmetic ,logic micro operation.                                                                                            | 04    |

|     | (c)        | Minimize the following function using tabulation method:                                                                              | 07    |

|     |            | $F(w, x, y, z) = \sum (1, 4, 6, 7, 8, 9, 10, 11, 15)$                                                                                 |       |

|     |            | OR                                                                                                                                    |       |

| Q.5 | (a)        | Design full subtracter with necessary derivation of functions.                                                                        | 03    |

| -   | <b>(b)</b> | Explain the following register transfer operation with the help of necessary diagram                                                  | 04    |

|     |            | T1: C < A                                                                                                                             |       |

|     |            | T2: C < B                                                                                                                             |       |

|     | (c)        | Assume A, B and C are 4 – bit registers.<br>Simplify the Boolean expression $F(A,B,C,D) = \Sigma(2,3,6,7,8,10,11,13,14)$ using K Map. | 07    |

\*\*\*\*\*