FirstRanker.com

www.FirstRanker.com

Enrolment FirstRanker.com

**Total Marks: 70**

## **GUJARAT TECHNOLOGICAL UNIVERSITY**

**BE - SEMESTER-III (Old) EXAMINATION - WINTER 2019** Date: 30/11/2019

Subject Code: 131101

**Subject Name: Basic Electronics**

Time: 02:30 PM TO 05:00 PM

**Instructions:**

- 1. Attempt all questions.

- 2. Make suitable assumptions wherever necessary.

- 3. Figures to the right indicate full marks.

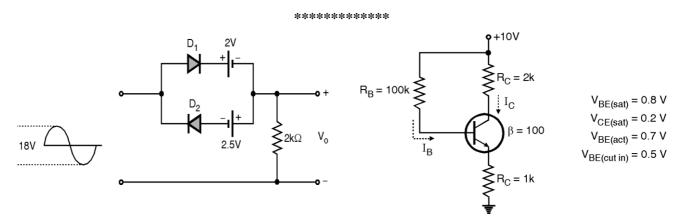

- 07 **Q.1** (a) Answer the following questions: 1) Sketch the piecewise linear characteristics of PN junction diode. 2) What is cut-in voltage? Write approx. value of cut-in voltage for silicon and germanium diode. 3) Define Thermal resistance. 4) Define Mean life time of a carrier. 5) What do you mean by PIV (Peak Inverse voltage)? Enlist the value of PIV for different rectifiers. 6) What is depletion region in PN junction diode. 7) Explain Zener breakdown phenomena. (b) Explain the Hall effect and obtain the expression of Hall coefficient. List the 07 applications of Hall effect. Draw and explain bridge rectifier circuit with capacitor filter. Draw necessary 07 Q.2 **(a)** waveforms. **(b)** The resistivity of intrinsic silicon is  $3 \times 10^5 \Omega$ -cm at 30°C. Calculate the intrinsic 07 concentration at 100°C. Assume  $\mu_n=0.13m^2/V$ -sec and  $\mu_p=0.05m^2/V$ -sec at 30°C. OR (b) A silicon sample is non-uniformly doped with donor impurity of  $10^{14}$ m<sup>-3</sup>. A 07 current density of 10mA/cm<sup>2</sup> is generated when electric field of 3V/cm is applied across it. Find the concentration gradient at 27°C. Given:  $\mu_n = 1500 \text{ cm}^2/\text{V-sec}$ . Draw the circuit of Common Emitter configuration of transistor. Explain input and Q.3 07 (a) output characteristics. Also derive  $\alpha = \beta / \beta + 1$ . For the circuit shown in Figure (1), explain working of the circuit and draw output 07 **(b)** waveform for given input signal. Also draw transfer characteristics.

## OR

- What is biasing? Why biasing is required for transistor? List biasing methods for Q.3 07 (a) transistor. Draw and explain the circuit of voltage divider biasing

- The silicon transistor used in the circuit of Figure (2) has  $VCE_{(sat)}=0.2V$ , 07 **(b)** VBE<sub>(sat)</sub>=0.8V, VBE<sub>(active)</sub>= 0.7V, VBE<sub>(cut in)</sub>=0.5V and  $\beta$ =100. (I) Show that the transistor is in saturation. (II) Calculate the value of RE for which the transistor just comes out of saturation.

- **Q.4** Define stabilization factors; S, S', and S". Also derive expressions for S and 07 (a) S' for self bias transistor circuit.

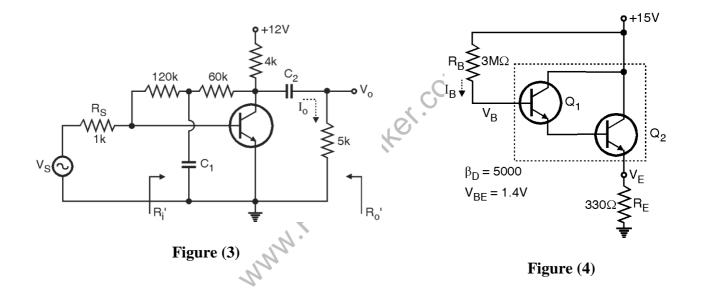

- The transistor used in the circuit of Figure (3) has the following parameters: *hie* 07 **(b)** = 500  $\Omega$ ,  $hre = 2.4 \times 10^{-4}$ , hfe = 60 and hoe = 1/40 k. Calculate : [1]Vo/VS [2]  $R'_i$  [3]  $R'_o$ . Assume all capacitors to be very large.

## OR

- 07 0.4 Draw circuit of an idealized class B push pull power amplifier and explain (a) its operation with the help of necessary waveforms.

- Calculate the dc bias voltages and currents for the circuit shown in Figure (4). 07 (b)

Q.5 st(a) Derive expressions for WWW. FirstRankein coms of CE hyperan FirstRankei. Com 07 follower circuit.

(b) Draw and explain working of diode compensation circuit for  $V_{BE}$  for selfstabilization in amplifier circuit.

## OR

- Q.5 (a) Draw structure of n-channel JFET and explain its working.

- (b) Draw a structure of p-channel MOSFET. Explain its working for enhancement type. Also draw and explain drain characteristics and transfer curve for the same device.

Figure (2)

07