**MARKS**

# **GUJARAT TECHNOLOGICAL UNIVERSITY**

BE - SEMESTER-VIII(NEW) EXAMINATION - SUMMER 2019

Subject Code:2181107 Date:09/05/2019

**Subject Name: Testing And Verification**

Time:10:30 AM TO 01:00 PM Total Marks: 70

### **Instructions:**

- 1. Attempt all questions.

- 2. Make suitable assumptions wherever necessary.

- 3. Figures to the right indicate full marks.

| Q.1 | ` / | Discuss verification versus testing. List and explain different level of abstraction in VLSI testing. | 03<br>04 |

|-----|-----|-------------------------------------------------------------------------------------------------------|----------|

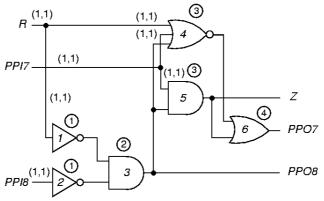

|     | (c) | What is combinational controllability and observability? Find                                         | 07       |

|     |     | controllability and observability for the following circuit.                                          |          |

| <b>Q.2</b> | <b>(a)</b> | Briefly explain different parts and features of ATE.                    | 03 |

|------------|------------|-------------------------------------------------------------------------|----|

|            | <b>(b)</b> | Write advantages and disadvantages of LSSD scan cell design.            | 04 |

|            | (c)        | What is Mux-D scan cell design? Explain in detail. Write advantages and | 07 |

|            |            | disadvantages of Mux-D scan cell design.                                |    |

#### OR

- (c) Define the term: failure mode analyses, failure rate, mean time between failure, mean time to repair, test vector, fault coverage, defect level.

- Q.3 (a) What strategy needs to be applied for verification? 03

- (b) List out different ad-hoc testing technique for VLSI. 04

# (c) Realize stuck at fault with example. 07

## OR

- Q.3 (a) What is Functional Verification?(b) Explain the importance of verification.03

- (c) The number of failures in 109 hours is a unit (abbreviated FITS) that is often used in reliability calculations. Calculate the MTBF for a system with 500 components where each component has a failure rate of 1000

- FITS.

Q.4 (a) What is compile code simulation?

03

- (b) Compare and contrast different Fault Simulation techniques.

(c) Explain serial fault simulation algorithm with an example.

07

- Q.4 (a) What is event driven simulation? 03

- (b) What is hazard? Explain cause and effect of different types of hazards. 04

- (c) Discuss different delay models.

(d) Discuss different delay models.

# www.FirstRanker.com www.FirstRanker.com Q.5 (a) List different types of test-bench and explain any one. (b) Discuss different technique for evaluation of logic elements. (c) Draw and explain test bench architecture. OR Q.5 (a) What is test bench?

\*\*\*\*\*\*

**(b)** Write a test bench for 4 bit shift register.

(c) Write a test bench for 4x1 de-mux.

www.FirstRanker.com

04

**07**