| Printed Pages : 4                                                  | 387      | NEC-501 |

|--------------------------------------------------------------------|----------|---------|

| (Following Paper ID and Roll No. to be filled in your Answer Book) |          |         |

| Paper ID :131501                                                   | Roll No. |         |

|                                                                    |          |         |

## **B.Tech**

(SEM. V) (ODD SEM)

# THEORY EXAMINATION, 2015-16

### **INTEGRATED CIRCUITS**

Time:3 hours]

[MaximumMarks:100

#### Section-A

- 1. Attempt all parts. All parts carry equal marks. Write answer of each part in short. (2x10=20)

- (a) Why don't we normally realize the betacompensated current mirror using MOS?

- (b) What are the basic blocks of phase-locked loop?

- (c) What do you understand by hysteresis voltage?

- (d) What is the role of coupling capacitor (C<sub>c</sub>) in IC 741 internal circuit?

- (e) Give the example of a square wave generator which utilizes positive feedback.

- (f) What is capture range in PLL?

(1)

NEC-501/11600

2

- **®** What is the chip number for phase locked loop?

- $\Xi$ Œ Define the term  $V_{III}$  and  $V_{IL}$  for the CMOS inverter. 000000000 represents 0 V, what output is The basic step of 9 bit DAC is 10.3mV. if

- Define noise margin for the CMOS inverter.

produced if the input is 1011011111?

$\odot$

# Section-B

Note: Attempt any five questions from this section.

(10x5=50)

simple current mirror circuit? Expalin with the help of a current mirror? How does it provide improvement over

Define the slew rate. Also derive the relationship between t, and slew rate for the IC 741

$\omega$

Sketch the properly labeled Master Slave D flip-flop waveform of the clock signal. circuit and explain its operation with the help of proper

4.

Give mathematical expressions in support of your What is a DAC? Describe the weighted resistor DAC

2

**NEC-501**

5

neat circuit diagram. What do you understand by the base current compensated

7.

- cycle. properly labelled circuit diagram and give mathematical Describe the Antoniou inductance simulation circuit with an output signal timer frequency of 700 Hz and 60% duty working. Design a 555 timer as an Astabel multivibrator with Draw the functional block diagram of IC 555 and explain its

- expressions in support of your answer.

œ

amp. What are the applications of sample and hold circuit? Describe the sample and hold circuit with the help of an op-

9.

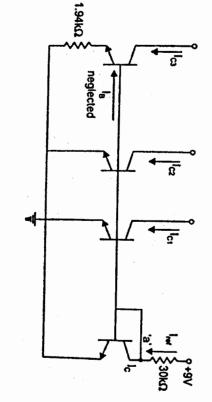

6 Determine Ic<sub>1</sub>, Ic<sub>2</sub>, Ic<sub>3</sub> for the circuit shown in figure 1. Assume  $\beta = 125$ .

Figure 1

MMMFilstRanke

P.T.O.

$\mathfrak{S}$

#### Section-C

Note: Attempt any two questions from this section.

(15x2=30)

- Describe the circuit for the KHN filter using three op-amp.

Design a second order butterworth low-pass filter having upper cut-off frequency 1kHz. Determine its frequency response.

- 11. Describe different regions of operation for CMOS inverter over its VTC characteristics.

Consider a CMOS inverter with following parametrs:

$$V_{\rm DD} = 3.3 \text{ V}, V_{\rm T0,n} = 0.6 \text{ V}, V_{\rm T0,p} = 0.7 \text{ V}, K_{\rm n} = 200 \,\mu\,\text{A/V}^2\,,$$

$$K_{\rm p} = 80 \,\mu\,\text{A/V}^2$$

Calculate the noise margin of the CMOS inverter circuit.

12. Describe the Schmitt trigger with the help of proper circuit diagram and transfer characteristics. A Schmitt trigger with the upper threshold level  $V_{\rm UT} = 0V$  and hysteresis width is 0.2V converts 1kHz sine wave of amplitude  $4V_{\rm pp}$  into a square wave. Calculate the time duration of the negative and positive portion of the output waveform.

(4) NEC-501/11600

MANN FIRST PAINTE