**R07**

# Set No. 2

# II B.Tech II Semester Examinations,December 2010 PULSE AND DIGITAL CIRCUITS Common to BME, ICE, E.COMP.E, ETM, E.CONT.E, ECE

Time: 3 hours

Code No: 07A4EC07

Max Marks: 80

### Answer any FIVE Questions All Questions carry equal marks \*\*\*\*

- 1. (a) Distinguish between sampling gates and logic gates?

- (b) Explain the operation of a chopper amplifier with neat block diagram and waveforms.

- (c) Distinguish between unidirectional and bidirectional gates. [4+8+4]

- 2. Regeneration is possible in the fixed-bias transistor flip-flop if the base-to-base voltage gain exceeds unity. Verify that this gain condition is satisfied provided that  $h_{fe}Rc > R_1$ . Assume that for each stage the current gain is  $|A_I| = h_{FE} \gg 1$  and that the input resistance  $R_i$  is small compared with either  $R_1$  or  $R_2$ . [16]

- 3. (a) Explain how a compensation circuit improves the linearity of a Bootstrap voltage time base generator.

- (b) With the help of neat circuit diagram explain the working of transistor current time base generator. [16]

- 4. (a) Prove that for any periodic input wave form the average level of the steady state output signal from an RC high pass circuit is always zero.

- (b) Explain how a low pass RC circuit act an integrator and what are the limitations? [8+8]

- 5. (a) Explain with relevant diagrams, the various transistor switching times

- (b) Explain the storage and transition times of the diode as a switch. [8+8]

- 6. (a) Draw the basic circuit diagram of a DC restorer circuit and explain its operation. Sketch the out put wave form for a sinusoidal input.

- (b) Draw the basic circuit diagram of positive peak clamper circuit and explain its operation. [8+8]

- 7. (a) Define positive level logic system and pulse logic system.

- (b) The transistor inverter (NOT gate) circuit has  $h_{femin} = 40$ ,  $V_{cc} = 12V$ ,  $R_c = 2.2k\Omega$ ,  $R_1 = 15k\Omega$  and  $R_2 = 100k\Omega$ ,  $V_{BB} = 12V$ . The input is varying between -12V and 0V. Assume typical junction voltages of pnp transistor. Prove that this circuit works as NOT gate. [16]

- 8. (a) With the help of a circuit diagram and waveforms explain frequency division of monostable multivibrator with pulse signals.

$\mathbf{R07}$

# Set No. 2

(b) A symmetrical astable multivibrator using germanium transistors and operating from a 10V collector supply voltage has a free period of 1000  $\mu$ sec. Triggering pulses whose spacing is 750  $\mu$ sec are applied to one base through a small capacitor from a high impedance source. Find the minimum triggering pulse amplitude required to achieve 1 : 1 synchronization. Assume typical junction voltage of the transistor and that the timing portion of the base waveform is linear. [16]

\*\*\*\*

**R07**

# Set No. 4

## II B.Tech II Semester Examinations,December 2010 PULSE AND DIGITAL CIRCUITS Common to BME, ICE, E.COMP.E, ETM, E.CONT.E, ECE Time: 3 hours Max Marks: 80

### Answer any FIVE Questions All Questions carry equal marks \*\*\*\*

- 1. (a) What is synchronization? What is synchronization on a one-to-one basis What is synchronization with frequency division? Give an example of synchronization with frequency division.

- (b) What is relaxation oscillator? Explain pulse synchronization of relaxation oscillator with necessary diagrams. [16]

- 2. Explain about the response of Schmitt Trigger to an arbitrary input signal with appropriate diagram. [16]

- 3. (a) What is a linear time base generator?

- (b) Write the applications of time base generators.

- (c) Define the sweep speed error, displacement error and transmission error of voltage time base waveform. [16]

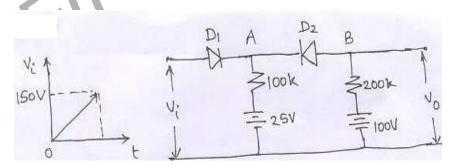

- 4. (a) The input voltage  $v_i$  to the two level clipper shown in figure 1 varies linearly from 0 to 150 V. Sketch the output voltage  $v_o$  to the same time scale as the input voltage. Assume Ideal diodes.

Figure 1:

- (b) Explain about positive peak voltage limiters above reference level. [12+4]

- 5. (a) Describe the switching times of BJT by considering charge distribution across the base region. Explain this for cut-off, active and saturation region.

- (b) Give the expressions for rise time & fall time in terms of trunsistor parameters and operating currents. [8+8]

- 6. (a) Draw the circuit diagram of Emitter coupled OR gate and explain its operation.

**R07**

# Set No. 4

- (b) Draw the circuit diagram of negative logic NOR gate and explain its operation.  $[8{+}8]$

- 7. (a) With the help of neat diagrams explain the working of bidirectional diode gate and derive the expressions to control voltages and gain.

- (b) For the bidirectional diode gate  $V_s = 25V$ ,  $R_F = 50\Omega$ ,  $R_L = R_C = 200k\Omega$  and  $R_2 = 50k\Omega$ . Find  $(V_c)_{min}$ ,  $(V_n)_{min}$ , gain A and the 3 dB frequency of the gate. [16]

- 8. (a) A symmetrical square wave whose peak-to-peak amptitude is 2V and whose average value is zero is applied to an RC integrating circuit. The time constant is equal to half -period of the square wave. Find the peak to peak value of the output amplitude.

- (b) Describe the relationship between rise time and RC time constant of a low pass RC circuit. [8+8]

Re

#### www.firstranker.com

**R07**

# Set No. 1

## II B.Tech II Semester Examinations,December 2010 PULSE AND DIGITAL CIRCUITS Common to BME, ICE, E.COMP.E, ETM, E.CONT.E, ECE Time: 3 hours Max Marks: 80

Answer any FIVE Questions All Questions carry equal marks \*\*\*\*\*

- 1. (a) Explain the response of RL circuit when a step input signal is applied

- (b) In a low pass RC ckt, R=2k $\Omega$  and C = 1 $\mu$  F =1.sv, 2ms, pulse is applied as input to this ckt sketch the output wave form. [8+8]

### 2. Explain the following

Code No: 07A4EC07

- (a) Storage and transition times of the diode as a switch

- (b) Switching times of the transistor.

- 3. (a) Draw the circuit diagram of discrete-component regenerative comparator.

- (b) Draw the transfer characteristic showing hysteresis. [16]

- 4. (a) Explain the operation of a six diode gate.

- (b) Write the applications of sampling gates.

- (c) Briefly describe the chopper amplifier and sampling scope. [16]

- 5. (a) What is phase delay and phase jitter?

- (b) Explain the method of synchronization of a sinusoidal oscillator with pulses.

- (c) Explain the frequency division in sweep circuit. [4+8+4]

- 6. (a) Explain transfer characteristics of the emitter coupled clipper and derive the necessary equations.

- (b) Draw the basic circuit diagram of positive peak clamper circuit and explain its operation. [8+8]

- 7. (a) Draw the circuit diagram of diode resistor logic OR gate and explain its operation.

- (b) The transistor inverter (NOT gate) circuit has a minimum value  $h_{fe} = 30$ ,  $V_{CC} = 12V$ ,  $R_C = 2.2k\Omega$ ,  $R_1 = 15k\Omega$  and  $R_2 = 100k\Omega$ ,  $V_{BB} = 12V$ . Prove that circuit works as NOT gate. Assume typical junction voltages. The input is varying between 0 and 12V. [16]

- 8. (a) Bring out the necessity and importance of current sweep circuits. List out its applications.

- (b) Determine the sweep error of the simple current sweep circuit. The component values in the circuit are  $V_{cc}=18v$ , L=150mH, the yoke resistance  $R_L=15\Omega$ ,  $R_S=10\Omega$  and  $R_d=150\Omega$ .

[8+8]

[8+8]

www.firstranker.com

Code No: 07A4EC07

\*\*\*\*

FRANKER

**R07**

# Set No. 3

[8+8]

### II B.Tech II Semester Examinations,December 2010 PULSE AND DIGITAL CIRCUITS Common to BME, ICE, E.COMP.E, ETM, E.CONT.E, ECE Time: 3 hours Answer any FIVE Questions

### Answer any FIVE Questions All Questions carry equal marks \*\*\*\*\*

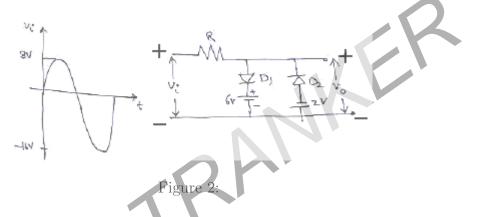

1. (a) Determine  $V_o$  for the network shown in figure 2, for the given waveform. Assume ideal diodes.

- (b) Explain negative peak clipper with and without reference voltage. [8+8]

- 2. What is a monostable multivibrator? Explain with the help of a neat circuit diagram the principle of operation of a monostable multivibrator, and derive an expression for pulse width. Draw the wave forms at collector and Bases of both transistors. [16]

- 3. (a) Explain the phenomenon of latching in a transistor

- (b) Define the following for a transistor switch

- i. Rise time

- ii. Fall time

- iii. Storage time

- iv. Delay time.

- 4. (a) Compare different logic families.

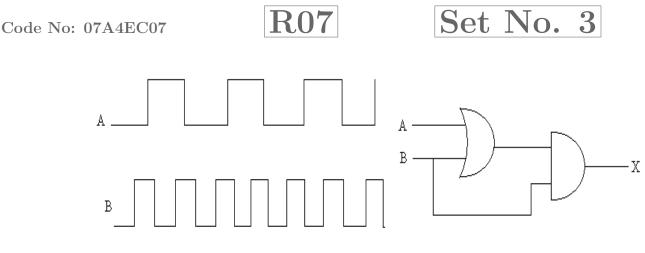

- (b) Draw the output waveform X for the given inputs figure 4b. [8+8]

# Figure 4b

- 5. (a) With the help of a circuit diagram and waveforms explain frequency division of an astable multivibrator with pulse signals.

- (b) Explain with the help of block diagram and waveforms for acheiving division of relaxation devices without phase jitter. [8+8]

- 6. (a) Draw the circuit diagram of the unidirectional diode gate with more than two inputs and explain its operation.

- (b) How do you overcome the loading effect of signal sources on control voltage?

- (c) Draw the circuit diagram of a sampling gate with more than one control voltage and explain its working. [16]

- 7. (a) Distinguish between Voltage and current time base circuits.

- (b) List out different methods to achieve a linear sweep voltage waveform.

- (c) Design a relaxation oscillator to have 3khz output frequency. Using 2N2646 UJT and a 20v supply. Calculate the sweep amplitude. The specifications from the data sheet are given as  $\eta=0.7$ ,  $I_p=2\mu A$ ,  $I_v=1nA$  and  $V_{EB,SAT}=3V$ . [4+4+8]

- 8. (a) Obtain the response of RC high pass cirucit for an exponential i/p signal.

- (b) A square wave whose peak-to-peak value is 1V, extends  $\pm 0.5v$  (0.5V w.r.t. to ground). The half period is 0.1 sec this voltage impressed upon an RC differentiating circuit whose time constant is 0.2 sec. Determine the maximum and minimum values of the O/p voltages in the steady state. [8+8]

\*\*\*\*