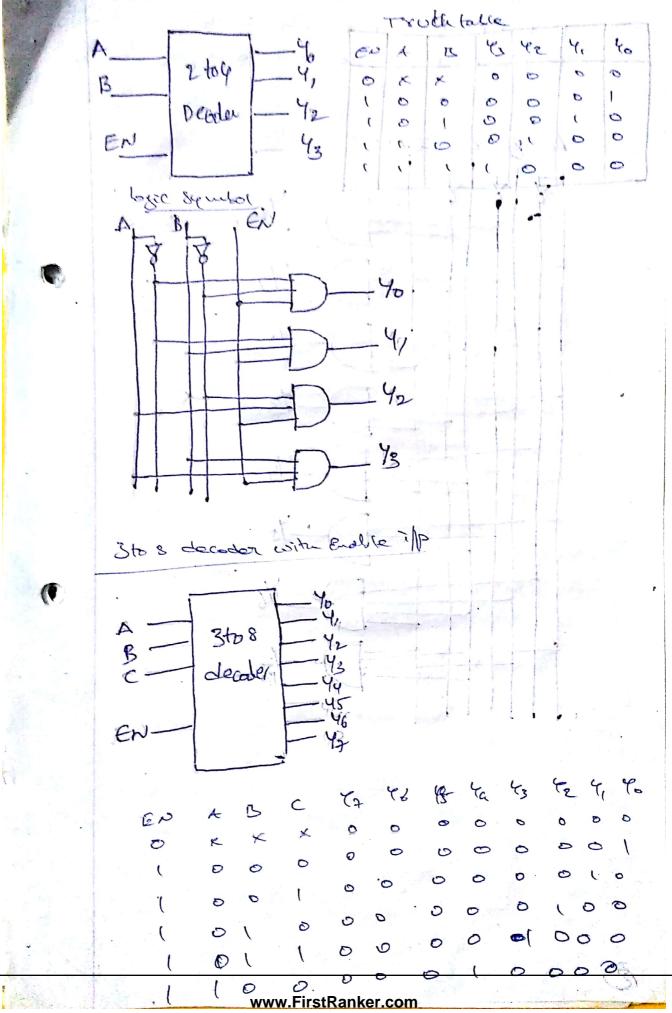

anker.com DESIGN -I www.FirstRanker.com www.FirstRanker.com Combinational logic crocuit is one whole drs depend only on its correct ilps. A combinational discust inang contain an arbitrary nort logic gates and inverters but no feedback loops. In combinational ciscuit, ANALYSIS we Start with a logic diagram & proceed to a formal description of the function performed by that ciscuit. Such as a trouble table or a logic Expression. Ju SENTHESIS are do the sevence, Starting with a formal description of proceeding to a logic diagram. 6 · DECODER A decoder is a multiple-ipp, and tiple-old logic circuit that converts coded ilp into coded opps, where the its & & of Goders are different. The 1/P code generally has ferred Sity them the of a code, of there is a one-to-one mapping from ilp code workdy into olp code workdy In a one-to-one pupping, each ilp code word produces a different of Gode word. www.FirstRanker.com

www.FirstRanker.com www.FirstRanker.com general structure & Decido mop of P Code word The most commonly used ill ade is an abit binary code, ashere an n-bit wood represents one of 2" dibberent coded volucia, normally the integers from 0 to 2"-1. The mast commanly used of p cade is a 1 oct of un todo which Contains in bits, where one bit is asterled at any time. E to 4 Decoder 40 ۲, 42 5 B ١ 0 0 0 0 0 2504 0 ۱ A 0 D 0 1 0 Decoder 0 42 0 D 0 0. 0 12 B ruta table Logic - Spubol John Structure B Yo 12 www.FirstRanker.com

# Firstfanker's choice

www.FirstRanker.com

Scanned by CamScanner

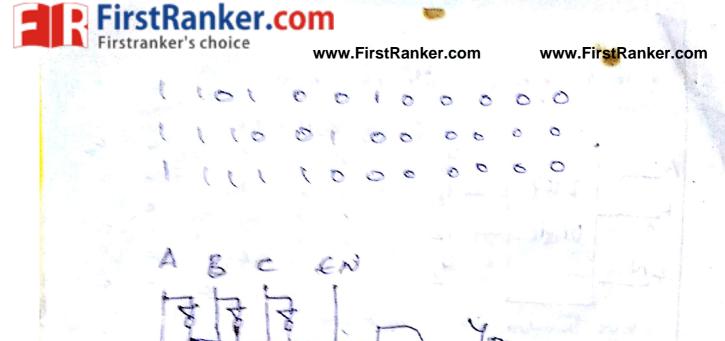

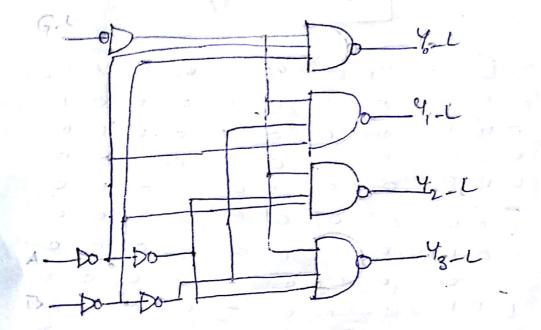

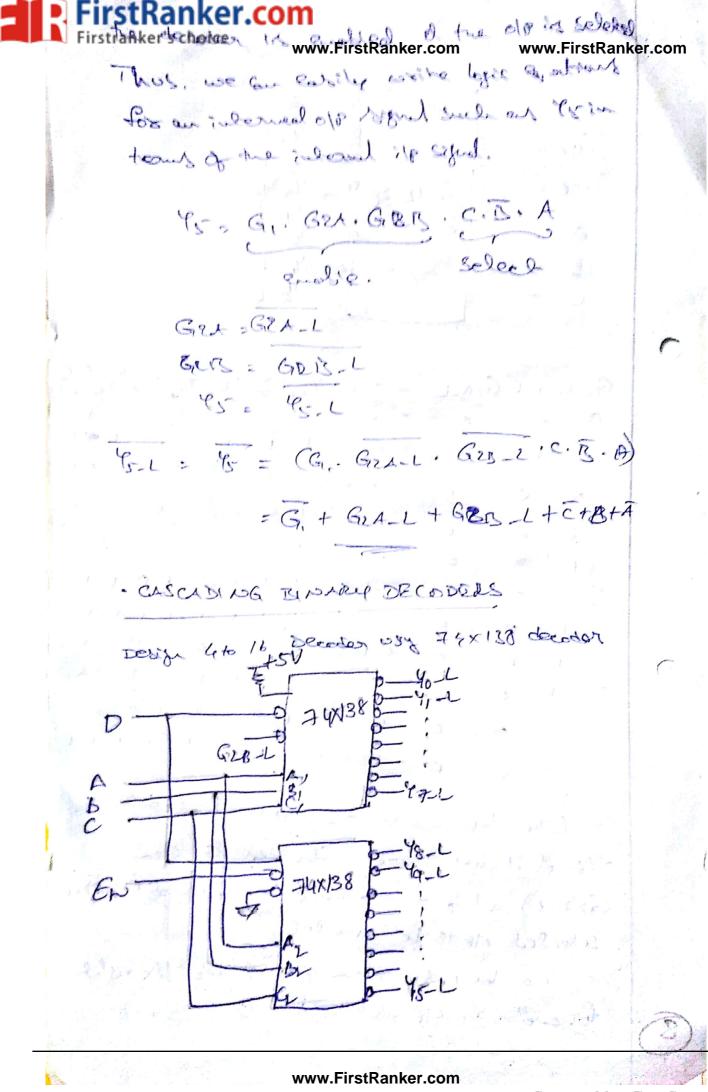

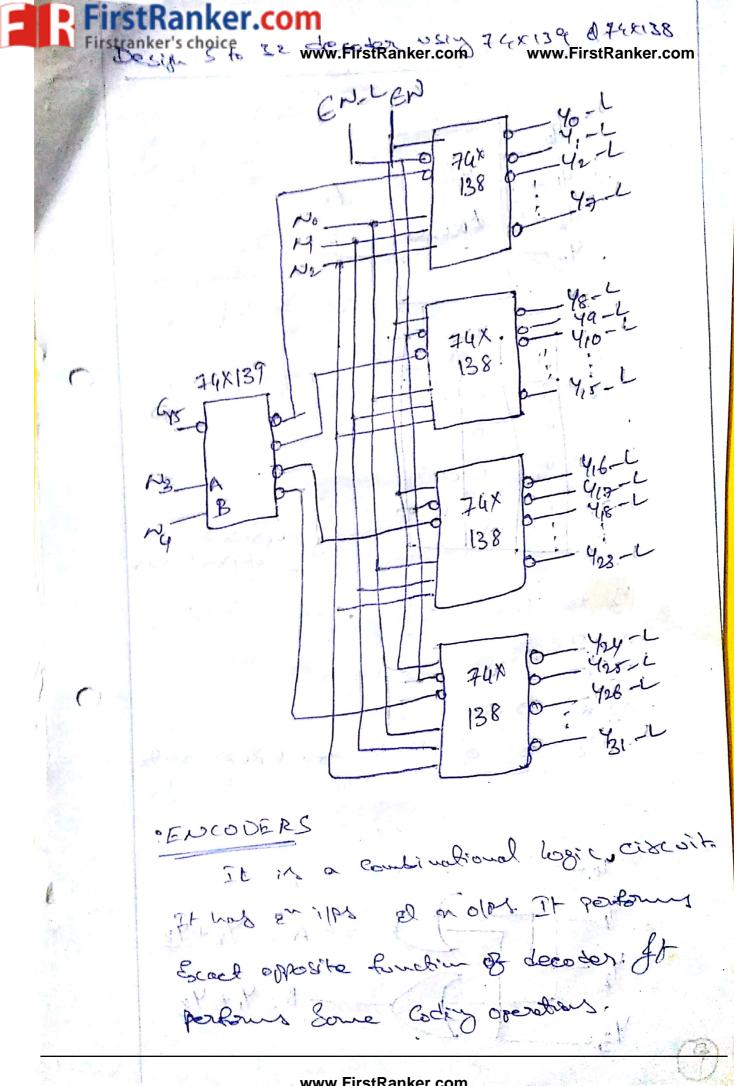

rstRanker.com anker's choice 8 Www.EirstRanker.com www.FirstRanker.com Design 3 to 8 decoder 2to 4 decoder Yo 4 A1 A 12 B B 43 ENI C 2toy Decoder .49 142 45 Br 46 47 END 40 4, 62 43 44 45 Ŷ. A 42 B 0 1 Ċ 0 O 0 0 D 0. 0 ( 0 0 O D 0 D 0 O 0 0 D 1 0 0 1 0 0 D 0 0 D 0 l ତ 0 0 1 0 0 0 0 Ţ D ľ 0 0 0 0 ( 0 0 e l 0 0 0 Ö 0 0 P 0 t 0 D δ 0 ſ O 0 1 0 0 Ó ( D 0 1. C 0 0 0 D F Ð 0 C 1 0 1 All and March MSI DECOPER 74×139 Dual Eto & Decodor 1/2 74×139 410 G, f 411 40 A1 412 BI Y, Yz 420 43 B G2 A2 421 422 Br 1 423 www.FirstRanker.com

Ranker.com

7-6

۱

www.FirstRanker.com 2

١

C

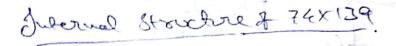

Two identical & independent 2 to 4 decodes are Contained in a Single MSI port the 74×139. The internal Strachere Strach that the of a the endle its of the 139 are active bus rost rist encoders were originally designed with active-low olds. Since TTL investig Jetes are generally Extertion non modely oves.

www.FirstRanker.com

Scanned by CamScanner

12

stRanker.com

C

C

www.FirstRanker.com

www.FirstRanker.com

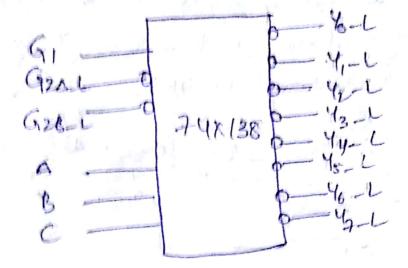

G. GRA-L G2O-L ABC 421 161 451 442 432 424-LA C 1 =11 XXX X ×  $\times$ X ( ( ( 0 000111 001 ( )( 1011 010 0111111 011 Ó 0 0 100 1110 0 0 101 0 011-1 6-00210 61,051111 D 0 0 0

Like the 74×1300 the 74×138 had activelow of PE El it has three enable iller (G1, G2A-2). G2B-L), all of which might be asserted tos the selected of to be accorded.

The logic function of 138 is Straight Excerd - an old in asported it d'alle it

www.FirstRanker.com

Scanned by CamScanner

1

www.FirstRanker.com

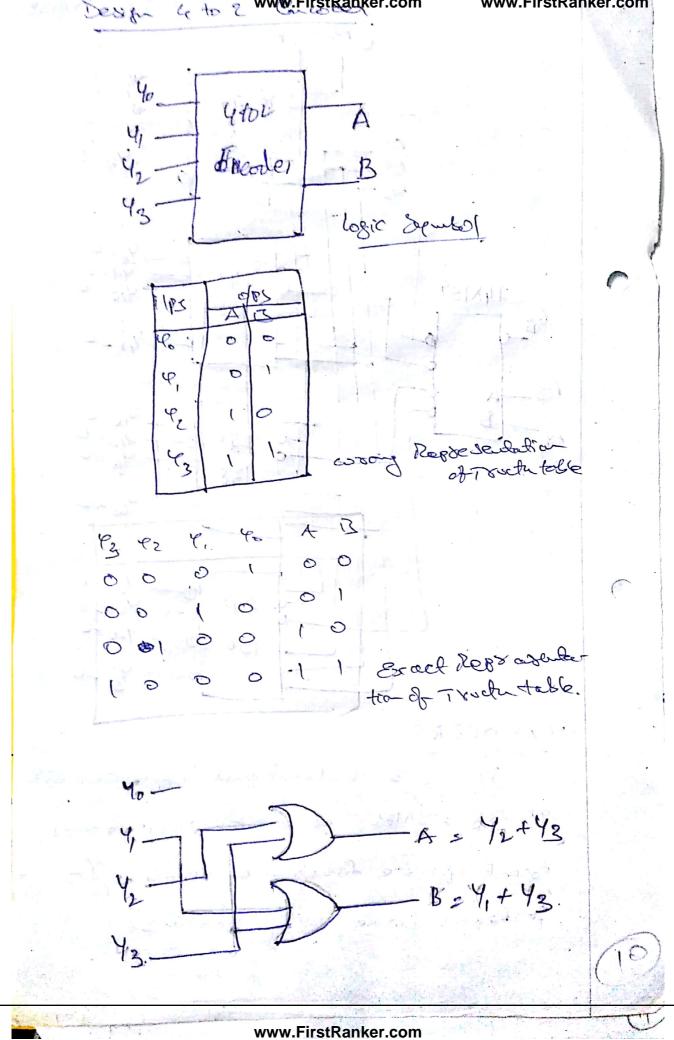

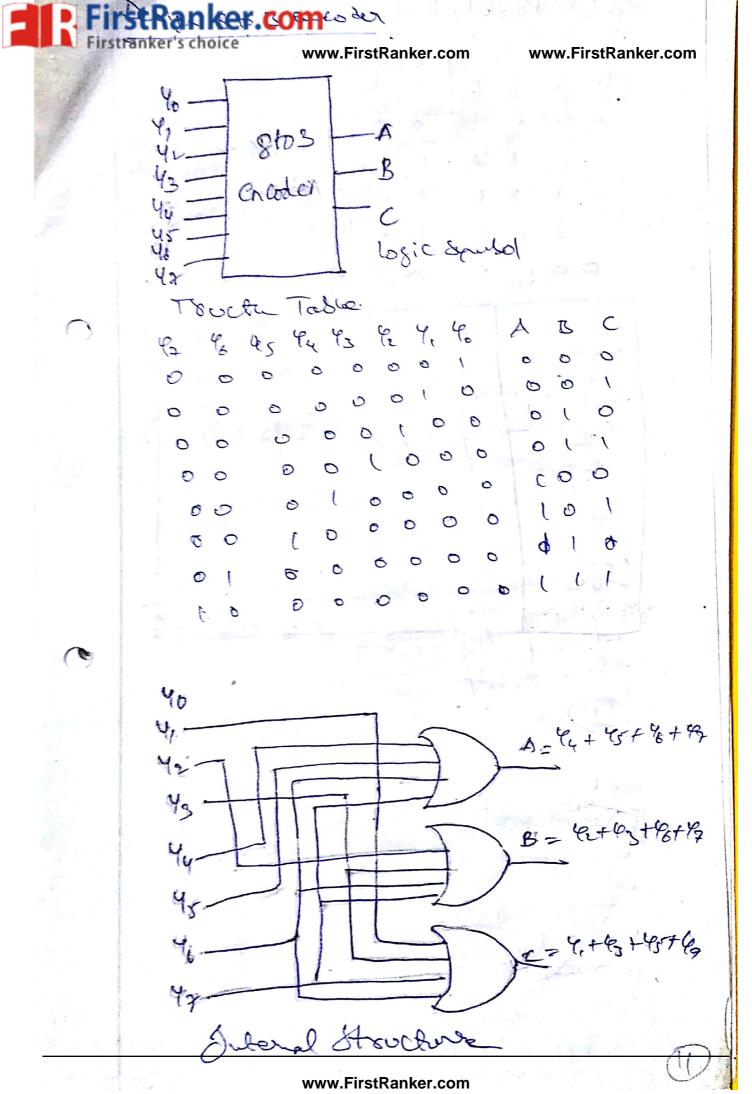

FirstRanker.<mark>com</mark> ranker's choice Ge to 2 www.FirstRanker.com

www.FirstRanker.com

Scanned by CamScanner

irstRanker.com

tranker's choice or www.FirstRanker.com

www.FirstRanker.com

www.FirstRanker.com

5

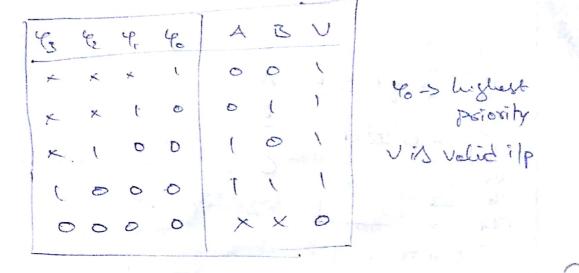

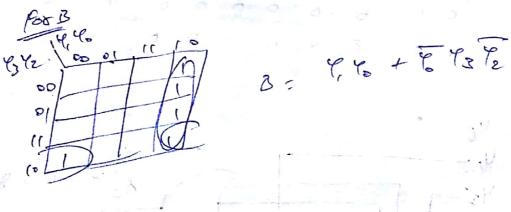

V= 40+4, +82+5

e mail

Scanned by CamScanner

12

-

Scanned by CamScanner

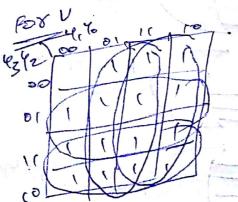

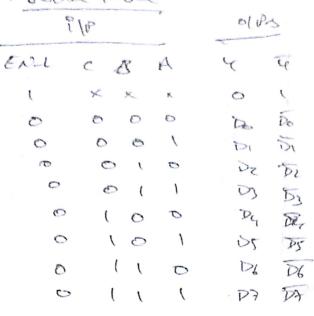

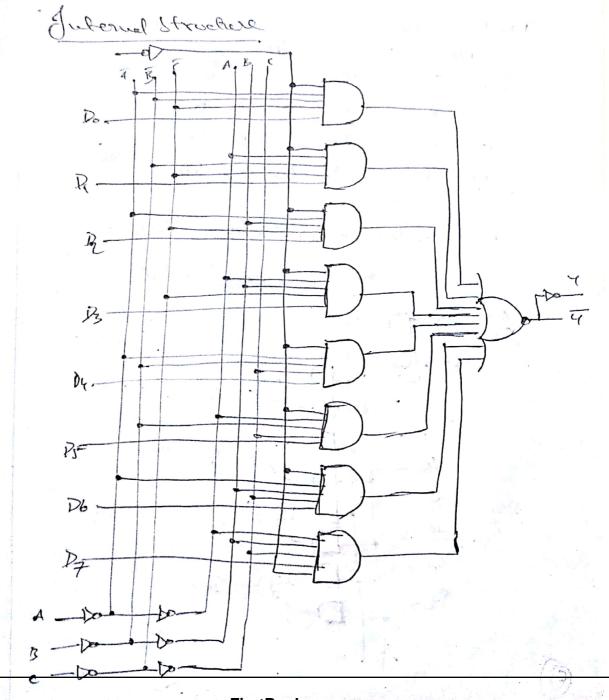

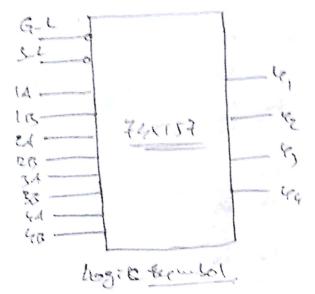

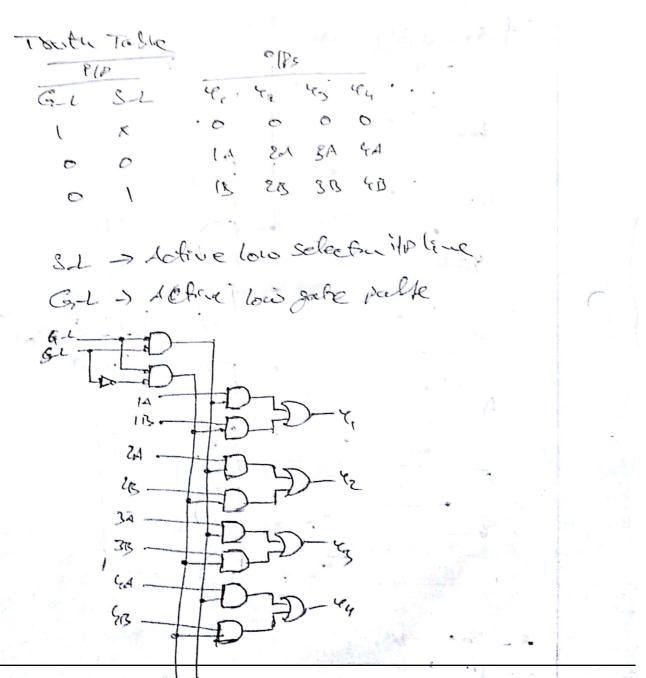

anker.com 's choice www.FirstRanker.com www.FirstRanker.com but no request if is accepted. Thus ha lawer priority 148 may be enabled. Trush Table ilpo OBS ELL SOL II-L JE IS IG IS IS IS IZ A. A. Go Go Go 1 ×·× D'I TELL 0 0 x x x x o x o o 0 1 0 xxx 0100 D × × 0 0 × K 8 0 0 0 0 0 x × O 1 ۱ 1 1 D 1 0 0 × C O 0 0 C ١ 1 1 1 MULTIPLEXERS & DEMOLTIPLEXEDS Mux. At is a competitudional logic circuit which has seerlin it it and it danly are output. n selection : 105 of 2 Date ; yould d only one ofp. Nox is also allel of deta selector(2) digital Switch. 5-0 1. Stand Sp ST. Four way Switch the state what we are

www.FirstRanker.com

FirstRanker.com www.FirstRanker.com

er's choice

www.FirstRanker.com

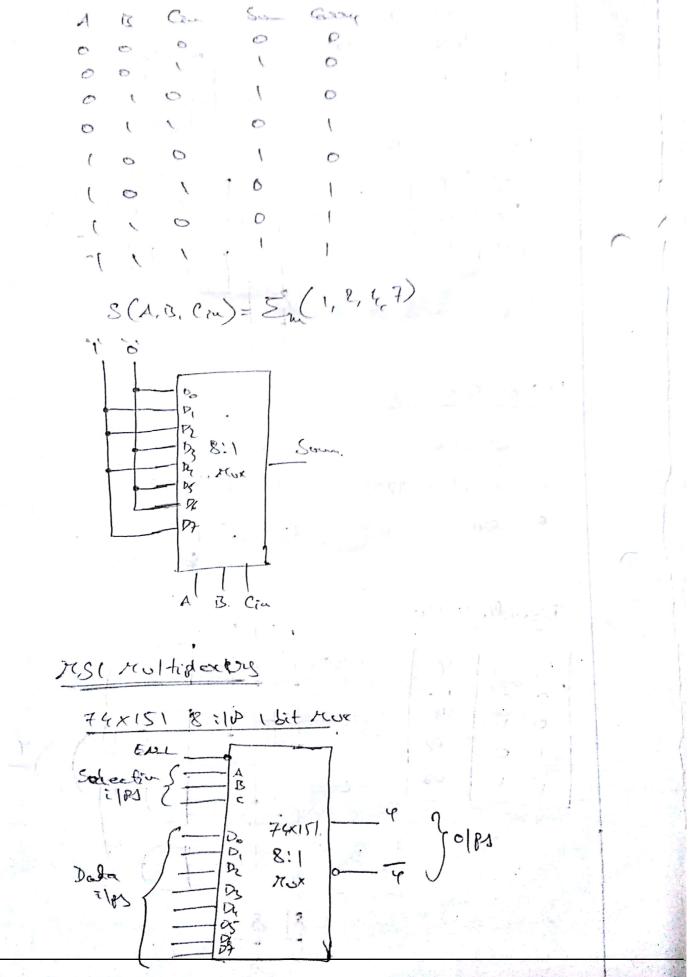

irstRanker.com irstranker's choice Realize Fullador www

Follador www.FirstRanker.com

www.FirstRanker.com

www.FirstRanker.com

C

er.com www.Firs

www.FirstRanker.com

www.FirstRanker.com

rstRanker.com

🍉 🖉 www.FirstRanker.com

www.FirstRanker.com

www.FirstRanker.com

www.FirstRanker.com

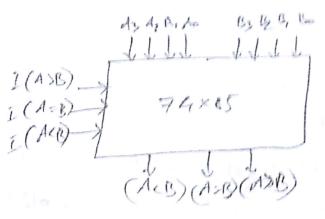

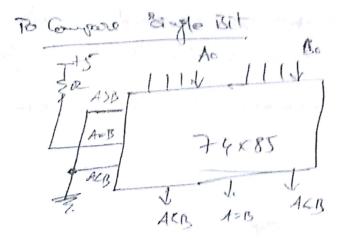

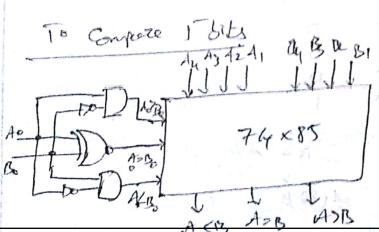

Compation is a Combinstrund Logic CICT Coliccle Courses two Brung Angul of any length of gives the appares result is g. greater time, logsten of Good to its off terripolo.

iles A \_ General \_ A>B HBS \_ HBS \_ A<B O[PS. HBS \_ A=B

6

As held are repressed by only one bit legt

| Reen |    | - Rock in the second |     |          |

|------|----|----------------------|-----|----------|

|      | TS | 433                  | ACB | A=0      |

| 0    | 0  | 0                    | 0   | 2-31 2 1 |

| 0    | ١  | 0                    | 1   | 0        |

| V a  | 0  | 1                    | 0   | 0        |

| 1    | ١  | 0                    | 0   | 1 ch     |

|      |    |                      |     |          |

the above touch table has four sourd. 2 = 2 = 4 50ws. where in its north star por ille. Bothe Flors must be equal legth.

(A(B) = AB

ADB = AOB

From the Touth table apartin a a (A>B) - AB

$(A=B) = \overline{A}\overline{B} + AB$

www.FirstRanker.com

www.FirstRanker.com

(ADR)

www.FirstRanker.com

Four Bit Compreter

This topic Bit Compander 2" = 2 = 256 could This The very compliated to Destyn by USI-g the above supreduce (Truth table field)

Hence to Sindiffe the design Compose two Eval weighted Sits from MSB to LSB Educatione the Conditions Jocaton, less el Equals.

A - As Az A. Ao Ro Br Br B. Ro

As the ill we have to compare Arelles Agens, the only we have to compare Arelles Agens, the only we have to compare Arelles The second wave to compare Arelles The second of the to compare Arelles

15B => A3>B2 + ×3 (42>B2) + Y3 X2 (A, >13) + X3X2X, (A>26) > Az Dz+ Xz Az Dz+ Xz Xz A, B, + Xz Xz KAOLO

www.FirstRanker.com

tRanker.com

A(B) =)

ALL IN THE REAL PROPERTY IN

www.FirstRanker.com,

(A=B) => KS 82 XIXA where x3 = A30 B3 X2 - ADBA Ko + A.OBO

MSI Comparation

www.FirstRanker.com

rstRanker.com

www.FirstRanker.com

www.FirstRanker.com

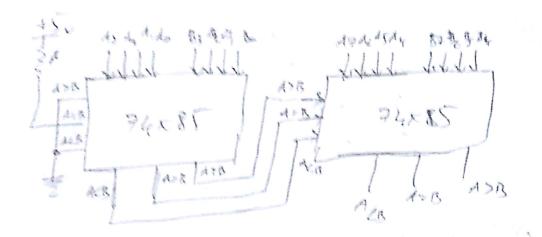

Derife 8-73 Combarly, ARA 244.82

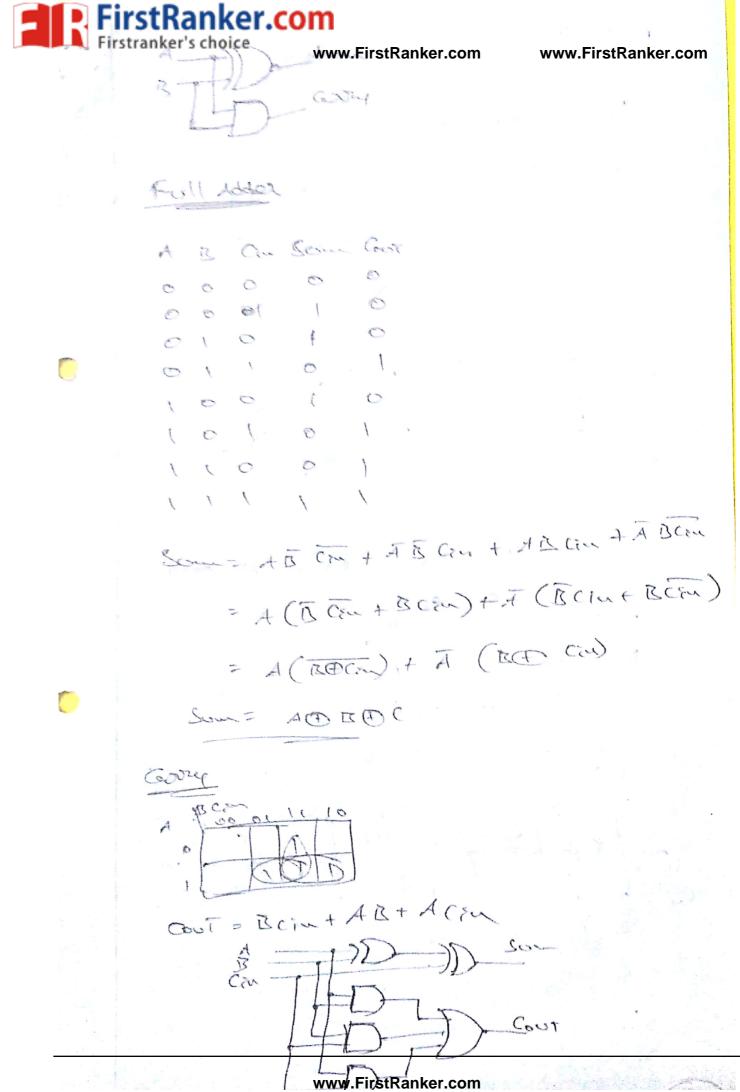

ADDERS

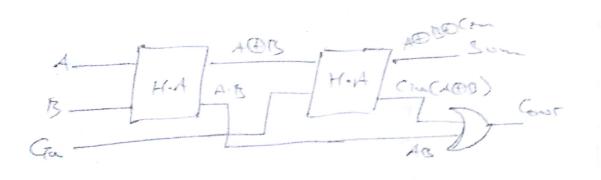

HALF Addens: FULL Addens.

Half adden it used to add two single sits of it Jewenthes sum of Carry olds. Full adder is que constructional citarily article is used to add two trusce single sits of its generates som it carry olds.

Malfadler

Carry =www.FirstRanker.com

Scanned by CamScanner

-

Simple Contended of the second definition of

4-bit parallel adder (Repole Gory Adder) A => A = A = A Ao B=> I, B2 B, Ho C4 53 52 5, 50 Be Az B: A, B3 A3 RG FARE FAR H-A F-A t CL 52

www.FirstRanker.com

www.FirstRanker.com

Æ

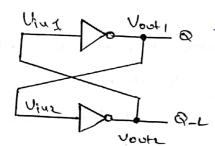

### BASIC BISTABLE ELEMENTS

The simplest sequential circuit consults of a paix of inverters bruing a feed back loop, as show in fig1. It has no impulse al two outputs, a and QLL.

Analysis. The cercuit of fig I is often colled a biblioble, since a strictly digital Analysis shows that it was had two stable states. If a is attight, then the bottom investor has a HIGH it of a Low off, which baces the top invertors of p HIGH as we also used in the fisht place. Bot if a ishow, then the bottom investor has a Low if of a HIGH off, which baces a Low if of a HIGH off, which baces a Low if of a Single state voriable, the state of signal, a, to decisible the state of the circuit there are two possible states, and a Q=1.

Fig1: A pair of inverters forming a bittable element. The bittable elevered its to simple that it has no imposes attractory no way. If contracting at changing its state when Power is first applied to the circuit, it sandomaly comes up in one state at the other and stand there obsever. Still, it serves core illustrative purpose very well, well, and well will actually show a coupled appli.

#### LATCHE & FLIP FIOPS

Latches et FlipFlops are the basic building blocks of most Sequential circuits. Typical disital systems use latches of FlipFelopes that are proparticized functionally specified devices in a standood IC. In Asic design environments, latches a FlipFlopH one typically Poedefined cally specified by the ASIC vended.

www.FirstRanker.com

Firstranker's choice www.FirstRanker.com Jop for a firstRanker's choice www.FirstRanker.com Jop FirstRanker.com Overtial device that normally simples its illes www.FirstRanker.com olv only at times setermined by a clocking Signal. On the other hand, most digital designers use the name batch

Los a Sequential device that watches all of its ips continuosly and Changes its ofps at any time, independent of a clocking signal.

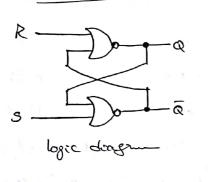

The NOR gate S-R latch

|   | 8  | R   | Qu              | Qutl     | State      |

|---|----|-----|-----------------|----------|------------|

|   | D  | 0   | 0               | 0        | No Change  |

|   | 0  | 0   | $\sim \sqrt{2}$ | ١        | NO CHANGE  |

| 9 | Ð  | V.  | 0               | 0        | Reset (0)  |

|   | 0  | ١   | Ν.,             | 0        | (asia (c)) |

|   | ×. | 0   | 0               | <b>1</b> |            |

|   | 1  | Ø   | 1               | Ň        | Set (1)    |

|   | X  | 1   | 0               | ×        | 1 1-1      |

|   |    | ) V |                 | ×        | Invalid    |

Trute table

The analysis of the operation of the active HIGH NOUR latch Can be summarized as follows.

NOR latch and it has no effect on the off State. Q and Q coll scincin in chatever State they were prior to the occurance of this input Gudition.

e. SET=@I, RESET=0: This will alway set Q=1, where it will remain even after SET seturns to 0.

3. SET= 0, RESET= 1: This will always selet Q=0, where it will semain even after RESE returns to 0.

4. SET=1, RESET=1: This Condition tries to SET & RESET the latch of the Same, dit produces  $P = \overline{P} = 0$ ; If the ilpore setured toders simultaniously, the resulting ofp Hale is seturatic el unpredictable. This of a Condition Should not be set off for forbidder (function)

www.FirstRanker.com

www.FirstRanker.com

(2)

| 5          | K  | ઙ | R            | a. | Qu+1          | state            |  |

|------------|----|---|--------------|----|---------------|------------------|--|

| O          | 0  | Ð | 0            | 0  | 0             | vochang          |  |

| 0          | 0  | 0 | 0            | X  | (             |                  |  |

| Ð          | 1  | Ø | 0            | D  | D             | Reset (0)        |  |

| ଚ          | ۲. | Ð | ۲ <b>.</b> ۲ | Ľ  | Ô             |                  |  |

| ί          | 0  | t | б            | Ð  | 1             | Set (1)          |  |

| L          | 0  | Ø | Ð            |    | $\sim \infty$ |                  |  |

| ٢          | ١  | ι | 0            | 0  | ⇒ (j          | Compland         |  |

| l          | l  | 0 | ١            | ١  | 0             | Compland<br>(Eu) |  |

| Taken Take |    |   |              |    |               |                  |  |

D later

| D           | Qu  | Quti |  |  |  |  |

|-------------|-----|------|--|--|--|--|

| 0           | 0   | 0    |  |  |  |  |

| 0           | - X | 0    |  |  |  |  |

| C.          | 0   | 1    |  |  |  |  |

| L           |     | N N  |  |  |  |  |

| Trota toble |     |      |  |  |  |  |

| Qu | Qut 1 |  |  |  |  |  |

|----|-------|--|--|--|--|--|

|    | Ð     |  |  |  |  |  |

| ١  | 1     |  |  |  |  |  |

| 0  | l c   |  |  |  |  |  |

|    | 0     |  |  |  |  |  |

|    |       |  |  |  |  |  |

|    | 0     |  |  |  |  |  |

www.FirstRanker.com

FirstRanker.com

erschliebes Anww.FirstRanker.com

www.FirstRanker.com

(tr)

SR FlipFlop

| <b>}</b> |       |   |   |

|----------|-------|---|---|

| Qu       | Quetl | ى | R |

| 0        | 0     | 0 | x |

| С        | ١     | ١ | Ø |

| t        | 0     | 0 | N |

| X.       | ١     | × | 0 |

| SK Flip Flop |       |      |  |  |  |  |

|--------------|-------|------|--|--|--|--|

|              | Qu +1 | 5 14 |  |  |  |  |

| e<br>2       | 0     | O X  |  |  |  |  |

| ð            | 1     | ι×   |  |  |  |  |

| E<br>N       | Ð     | X I  |  |  |  |  |

|              |       |      |  |  |  |  |

|              |       | X U  |  |  |  |  |

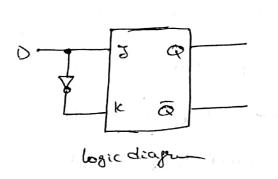

D Flip Flop

| Qn | Quti | D |

|----|------|---|

| 0  | 0    | 0 |

| 0  | ł    | t |

| l  | 0    | Ð |

| ι  | C    | ١ |

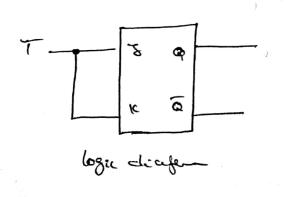

T - Flip Flop

| Qu | Queti      | 7        |

|----|------------|----------|

| ٥  | Ø          | 0        |

| Ð  | ́ <b>х</b> |          |

| Ņ  | Ø          | $\sim 1$ |

| L. | N          | ð        |

For the design of Sequendial citicating we should know the Excitation tables of Flip Flops. The Excitation table of a Plip Flop Can be obtained from its truth table. It indicates the imputs sequired to be applied to the flip-flop to take it from the present state to the next state. The truth tables of Excitation tables of Verious flip-flop one give above

#### www.FirstRanker.com

Fiptrartyes's Choice www.FirstRanker.com

www.FirstRanker.com

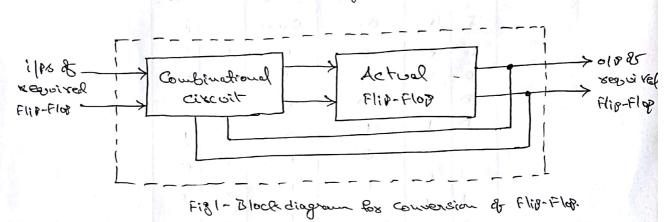

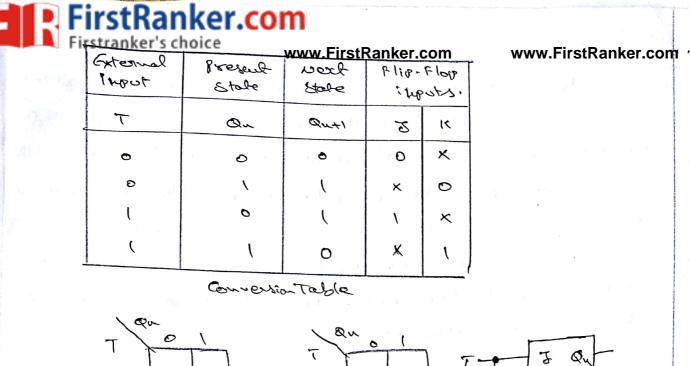

To convert one type of flip-flop into another type, a Constructional circuit in designed such that it the inputs of the sequenced plipeflop (along with the olds of the actual Flip. Flop it seavered) one feel as ilps to the combinational circuit and the output of the combinational circuit its connected to the inputs of the actual flip flop, then the old of the acatual flip flop is the els of the required flip. flop. In other words, it means that, to convect one type of flip-flop into another type, we have to obtain the expression for the ilps of the existing flip-flop in terms of the ilps of the reavised flip-flop d the present flip-flop in terms of the ilps of the reavised flip-flop d the present flip-flop in terms of the ilps of the reavised them. The approximate is shown in fig 1.

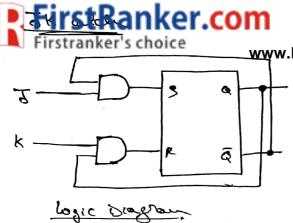

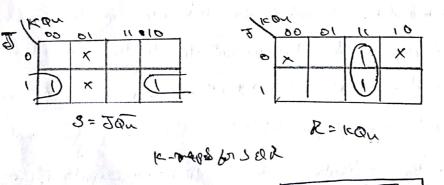

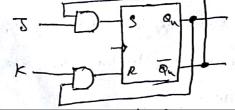

S-R Flip Flop to J-K Flip Flop

Here the External iPs to the alseady available S-R Flip. Flop will be 3 K and K. 3 and K are the olds of the Combination and circuit, which are also the actual ilps to the S-R elid-flop. We write a truch table with IK, On, One, S, and R, where On in the proper Steps of the flip flops of One is the procent Steps of the flip flops of One applied, i.e., On denotes the glade of the flip-flop before the applied of the illes of our selects to the State State flip.

www.FirstRanker.com

FirstRanker. Compare eight combinations, For Listranker's choice of SWWW. FirstRankef.cont the www.FirstRankericom Out, i.e determine to which need the (Out) the JK F-lip Plop will go from the present these On it the proceed if it is all a are applied. Now complete the table by write of the values of S el & required to get each and from the Cossesponding On, i.e. write what values of S el R are required uited to change the state of the PROP-Plop & from Anto Out!

The conversion table, the K-raps for Sel & in tours of J, K el On and the logic diageon Showing the Conversion from S-R to Z-K & are Shown in Fig-2

|               |                                         | <u></u>                                                           |                                                       |                                                       |

|---------------|-----------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|

|               | Present<br>State                        | Next<br>State                                                     |                                                       | puts.                                                 |

| 15            | Q~                                      | Quti                                                              | ٌ ی                                                   | R                                                     |

| 0             |                                         | 0                                                                 | 0                                                     | ×                                                     |

| 0             | stat 1                                  | <ul> <li>√ 2.</li> </ul>                                          | X                                                     | 0                                                     |

| ° <b>\</b> ⇔' | · · · O · · ·                           | 0                                                                 | 0                                                     | ×                                                     |

| 1             |                                         | 0                                                                 | 0                                                     | l                                                     |

| 0             | 0                                       |                                                                   |                                                       | 0                                                     |

| 0             | (                                       | 1                                                                 |                                                       |                                                       |

| 1             |                                         | gr i strat                                                        | X                                                     | Ø                                                     |

| 1             |                                         | (                                                                 | L.                                                    | 0                                                     |

| , t           |                                         | O                                                                 | 0                                                     | $[N_{i}]$                                             |

|               | 000000000000000000000000000000000000000 | 14 State<br>17 Qu<br>0 0<br>1<br>1 0<br>1<br>1 1<br>0 0<br>0<br>0 | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

Conversion table

Fig-2 Logic deagler

## IrstKanker.com

# Inkto's Doiger & 100 www.FirstRanker.com

www.FirstRanker.com

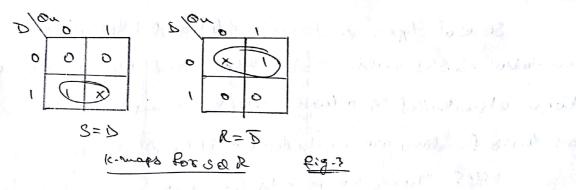

Here S-R flipflop is available & we could the overation of the D Flipflop from it. So Dis the External ilp of the olops of the Could control circuit are the ipper to the available S-R flip-flop. Exposed the ilps of the existing flip-flop Sold in terms of the External input D of the present state On.

The conversion table, the 10-maps for SER interns of D & Qu, and the logic diagram showing the conversion from S-R to D are shown below figs.

|                    | ľ               |       |   |                |               |

|--------------------|-----------------|-------|---|----------------|---------------|

| Externel<br>Juputs | Poesal<br>State | state |   | sflop<br>Buts. |               |

| D                  | On              | Quti  | S | R              | D-S PR-       |

| 0                  | 0               | 0     | 0 | x              |               |

| 0                  | They a          | Ð     | 0 | 1              | - An-         |

|                    | 0               |       | t | 0              |               |

|                    | Contractor      |       | × | 0              | logic diagrom |

J-K 2118 flop to T Plip-flop

Here J-K flipflop its available of we want I findflop operation from it. SO T its the External ilpel I el Kare the actual inputer to the Existing Flip-Flop. Tel On make Boox combihelions. Express Jelk interno & Taxel Qu.

The conversion table, the k-maps for 5 d k interns of T of Qu, to and the logic diagram showing the conversion from 3k to Tare Show in fight.

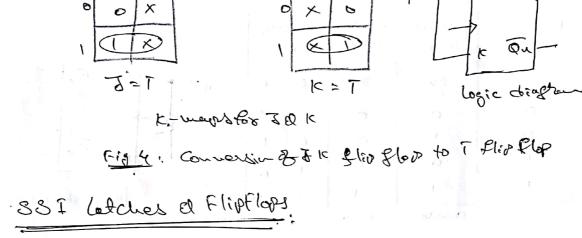

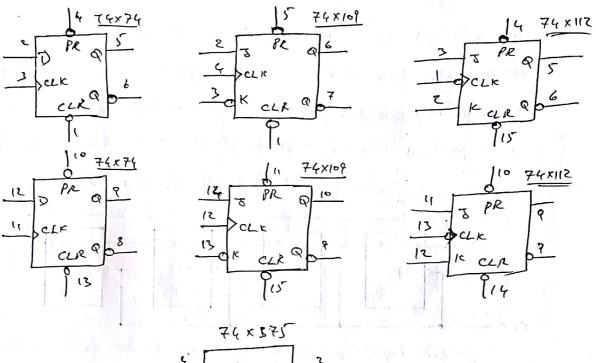

Several types of descrete Calches & Flip Flops are available as SSI parts. SSI Catches and Flip Flops have been elimitheted to a large Extent in modern designs as their functions are embedded in BLDs & FPGAI.

Fig-5 Shows the princips for several SSI sequencial devices. The only tatch in the figure is the Flex 375, which containy four D tatches, Similar in Auntaian to the generic" D tatches. Because of pin limitation, the tatches are avanged in paixs with a Common C carbod line for each pair. IS)

stranderischpicetre devices in fings the most interstranker.com is the 74, x7x, which contains two independent positive-edge triggered D-flip flops with preset il clear inputs.

stRanker.com

0

The 74×109 is a positive-edge-triggered 3- TO Plip Plop with an active low its (named To 31 K-L). Another JK Flip Flop is the 74×112, which has an active-low clock if.

Figs: poincubs for SSI befores & Clip Plaps

www.FirstRanker.com Scanned by CamScanner

CLK

www.FirstRanker.com

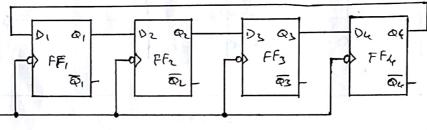

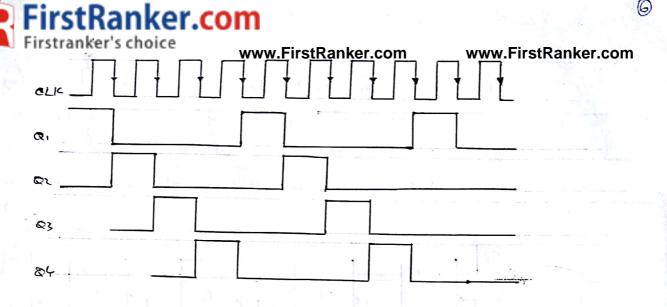

Ring Coulor: This is the Simplest Shift Register Coulor. The basic king Coulor Using D FFS is show Fig 6. The sealidation of this Counter Using J-K FF2 is show in fig 7. Ats guese diagram of the sequence table Shan in fig 8. Ats timing dagton is shore in fig-9. The PhipPlas are arranged as in a more all shift sequester, i.e. the Q off of each stoge is connected to the Dilp of the next stoge, but the Q olp of the best FF is Connected back to the Dilp Q the to first FlipFlop Such to that the array of FlipFlops is arranged in a sing Q there fore, the next Sing Coulor!

fig: 6 Logic diagram of a ke-bit King Counter wing D-flipplops

fist: Logic diagram of a k-bit Ring Counter Using J-k flive Flops

|               |           |      | A   |               |

|---------------|-----------|------|-----|---------------|

|               | Q, Q2     | ©3   | ભ્પ | After Clock   |

| (1000)        | $( \circ$ | 0    | 0   | 0             |

|               | 0         | D    | ð   | L Contraction |

| (000) (0100)  | 0 0       | s (  | ð   | . ک           |

|               | 00        | 0 0  | N   | 3             |

| 00104         |           | 0 0  | 0   | ų             |

|               | 0         | 0    | 0   | 2             |

| State dragson | 0         | 0 1  | D   | 6             |

|               | 0         | 0 0  | •   | 7             |

|               |           | 1.12 | 1.1 | Talle         |

Fig 8: Stole doging & segrere type www.FirstRanker.com

Fig 2: Timing diagram of a ke-bit sing counter.

An anost instanced, only a single 1 is in the register and is made to circulate around the seguitter as long as chock Pulses are applied. Juitially, the fight FF is present to a I. So, the initial state is 1000, i.e. Q=1, @2=0, Qz=0, & Qu=D, After each clack Polse, the centers of the regater are shifted to the right by one bit and Qy is shifted back to Ry. The sequence repeated after four clark Edites. The nont distance states in the sing counter, i.e., the rob of the ving counter is equal to the world Firs used in the counter, An or-bit sing counter can count only a bits, where as Ar-bit sipple couldry Can could 2" Lits. So, the sing could an count endy a tity, is a economical compared to a tipple counter, but has the advantage of requiring no decoder. Since we Can sead the Court by Simply noting which FF is let. Since it is entirely a sign chronous operation it requires no gates external to FFS, it has the muchan Further advantage of being very fast. Johnson Counter: (Twisted Try Counter)

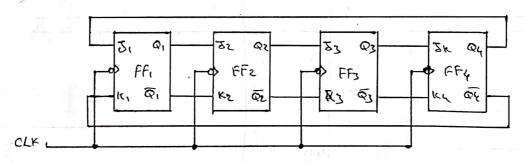

This could is obtained from a serial in Serial out Shift segister by Providing feedback from the inverted output of the last FF to the Dinget of the First FF. The Q alpot each stage is connected to the Dip of the next stage, but the Q alpot of the last stage is connected to the Dip of the lift of first stage, therefore, the C www.FirstRanker.com

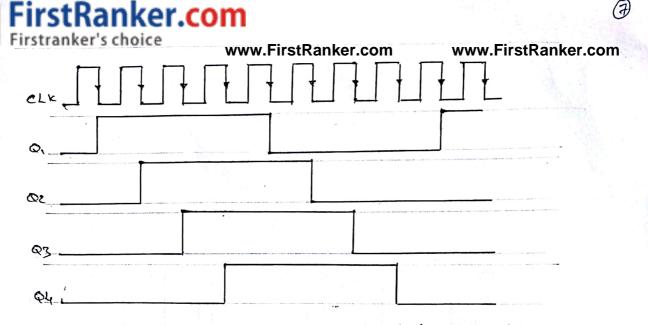

Kanker comton. This feed back arrange mult Produced a ourgove segure. FirstRankersom www.FirstRanker.com The logic diagram of a 4-bit Johnson Counter Using Drig is show in fig 10. The scalization of the Sound Using JK FE, 13 " Phone in Eyre. The prove diagram of the sequence table able Show in Fyrz. The timing dealer of a Johnson Counter is than in fig 13. D, Q, 2 94 Du DZ FE FFr FB FF4 ିର୍ 9, CLK Figio: Logic diagram of a 4-bit twilted sing counter usey D FFE. 31 Q 12 23 Q3 **ک**دہ FR FFS FFZ FF4 Q, Q ĸ, \$ Qu CLIC Fig 11: logic drageon of a 4-bit twitted ting comber using IK FFS Q, Q2 Q3 After Clack  $Q_{L}$ 000 6000 0 011 5 1100 1110 7 @ Stake drage C 0 Esequence take Figure state dragen & Secure take of a torrer sing Carter Let initially all the FFI be served, ie; the state of the couler be 0000. After each clack putse, the level of Q, is thisted to Q2, the level of Q2 to Q3, Q3 to Q4 and the level of Q4 to Q, and the sequence given in Right obtaind. This sequence is rep-

eabel after every eight check potres, www.FirstRanker.com

Fig 13: Thuring diagram of a 4-bit twisted sing counter

An on FF Johnson Couster Can have 2n cuigue States of Can Coust up to 2n polses. So it is a mod-2n Couster. It is moke economical them the normal sing Counter, but less economical them the dipple Coulor of treevoired two its gales for decoding regardlets of the Side of the Coulor. Thus, it services more decoding circuitary them that by the normal sing Counter, but less their that by the ripple Coulor. It represents a middle ground between the sing Counter of the ripple Counter.

## Basic Sequential Logic Design Steps

The procedure for designing synchronous Sequential citaits Can be summarized by a list of recommended steps. 1. From the world description of specifications of the desired operation, desire a state diagram for the circoit.

2. Reduce the number of States if we cessivy.

3. Assign binary values to the States.

4. Obtain the binary- coded State table.

5 Choose the type of flip-flops to be table.

6. Derive the simplified plip-plas input equations of alls equalizers

7. Dracs the logic diagram.

www.FirstRanker.com

Scanned by CamScanner

stkanker.com

www.FirstRanker.com

www.FirstRanker.com

(9)

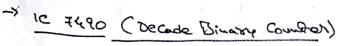

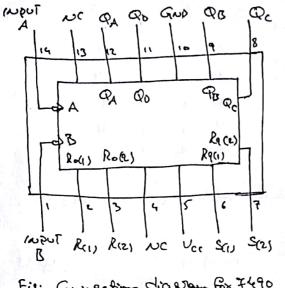

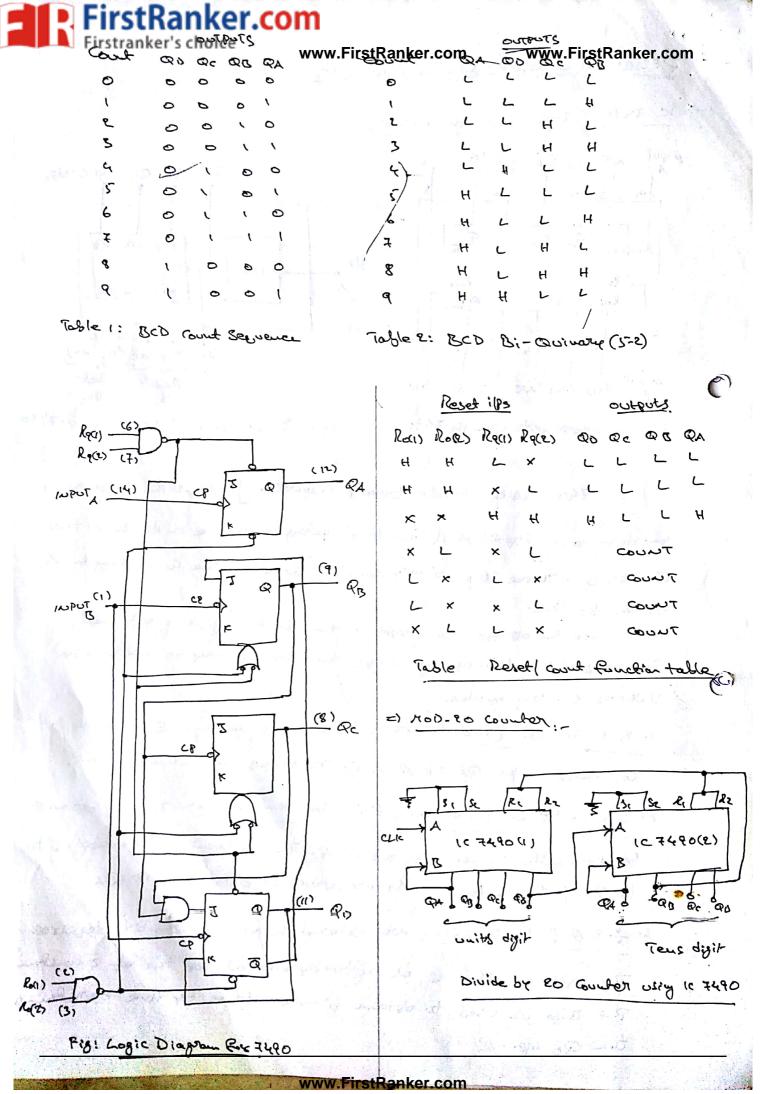

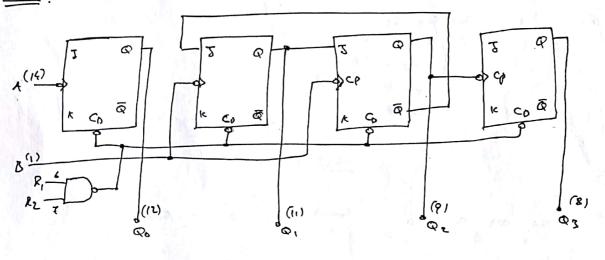

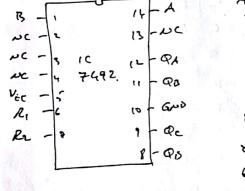

Fig: Connection diagram for 7490

8

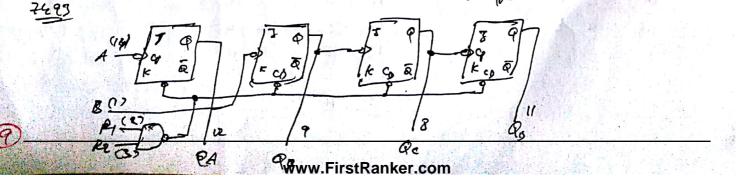

Fig: Basic internal structure of 7790

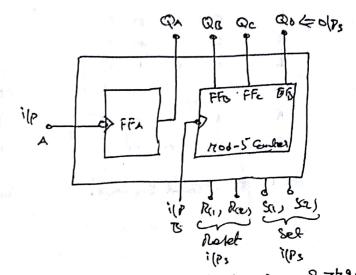

IC 7400 is a decode binory counter. It consists of four master-Slave Flip-flops of additional gating to provide a divide by two Comber d'a ture Stafe binary comber for cohich the court length it devide -by- five.

Since the OB from the divide by two Section is not juternally Connected to the succeeding stages, the devices may be operated in Vations Country modes.

1. BCD Decade (8421) Counter. The 3 ilp with be Esternally Connected to the QA OP & A ilp receives the incoming count.

2. Symmetrical Bi- quinary Divide by - Ten Counter: The QD of must be Externally connected to the A ill. The ill count is then applied to the B ile & a the ? to service whe is obtained at old QA.

3. - 20 - 5 Counter: No Octomal inter connecting are required. The FIRST FF it used as a binary element for the de 2 fouching. The Bip is used to obtain binong divide by five operation of the Qo of.

Scanned by CamScanner

# Kanker.<mark>co</mark>m

# rstranker's the PS CA-www.FirstRanker.com

#### www.FirstRanker.com

9

The The The & These are high speed high type type Counters Portitioned into two sections. Each counter has a divide by two Section a cituar a divide - by- sir (7492) or divide - by - eight (7493) Seefre collich are triggered by a High to low transition on the clock 1/ps. Each section cambe used separaholy at ties together to form divide-be-twelve & divide-be- Sixteen Courtons.

7492 -> - 12 couler 7493 -> -16 Courses

Bach device consitter & four matter scale Flip flops which are internally connected to Provide a - 2 soufran.

7492

metris of man

and give

#### Modes 027692

1. Mob-12: The B ip west be Externally connects to the QA ofp. The A is teceives the incoming could QU produces a symmetrial ? 12 Square wave of 2. : 2 El : 6. no External intered - Course chung are required, The EXXI of My user as a binning clanut For the & 2 for. The & prilipid used to obtain the = 3 growhin that the Qgel Qc O/ds. el dividesy six operation at the of of ps

Scanned by CamScanner

EirstRanker.com

| TIKI  | and the second | 2 14 | vice. |

|-------|----------------|------|-------|

| HR2 - | 3 10           | 12   | - Q1  |

| NC -  | 4 749          | 3 "  | -90   |

| Uce-  |                | (*   | GND   |

| NC -  | 6              | 9    | - 90  |

| 10C - | 7              | 1    | Qe    |

www.FirstRanker.comor: The Www.FirstRanker.com Connected to itp 8. The ilp court pulses are applied to the ilp A. Simultaniously divisions & E. L. 8 & 16 are performed at the QA, QA, QC O QD of parshown in the truth table.

2. 3-bit Ripple Counter: The ilp count puters are applied to the A. Simultaniously frequency divisions of Z. C. d. 8 are available at the PB OC DOD with keypeak to & the 3-bit tipple through Counter.

7492 2 7493

| Reve | e :10    | 052         |

|------|----------|-------------|

| R.   | Rz       | QA QD QC QD |

| 4    | l¢       | LLLL        |

| L    | н        | Count       |

| +    | ر        | Consult     |

| L    | <u> </u> | Count       |

|      |          |             |

7492

7493

|         | Court      | Q.L            | Фk | Oc      | 9        |                        | Count          | Q.       | 00 | . Q.   | G     | 20          |

|---------|------------|----------------|----|---------|----------|------------------------|----------------|----------|----|--------|-------|-------------|

|         | 0          | L              | L  | L       | Ľ        | 0000                   | ø              | L        | L  | L      |       | <u> </u>    |

|         |            | ન              | L  | L       | Ĺ        | 1.008                  | 1              | H        | L  | L      | د     | -           |

|         | ٤          | L              | н  | L       | L        |                        | ۲              | L        | H  | C      | L     |             |

|         | 3          | H              | н  | L       | Ľ        | 21                     | 3              | <b>H</b> | ધ  | ٢      | L     |             |

|         | 4          | Ĺ              | ٢  | 4       | L        |                        | 4              | HL       | L  | н      | L     | • 1 .       |

| p perte | S          | H              | L  | H       | L        |                        | ſ              | H        | 5  | , H    | L     |             |

| and the | 6          | L              | L  | L       | н        |                        | 6              | ₩L       | Н  | н      | L     |             |

| Aurice  | 1.7.       | 4              | L  | L       | н        | 1.120                  | 7              | н        | н  | Н      | L     |             |

| st ist  | 8          | L              | ભ  | L       | н        |                        | ٢              | L        | L  | L      | н     | The second  |

| abiuk   | e          | #              | н  | L       | н        |                        | ٩              | н        | ٢  | L      | ч     |             |

|         |            | 14 . 1         |    | ě, i    |          |                        | 10             | L        | 4  | L      | н     |             |

|         | (•         | L              | L  | н       | (4       |                        |                | H        | н  | L      | H     |             |

|         | ts -       | 4              | 1  | #       | 4        | the faither            | 12             | L        | L  | н      | H     | , and inc.  |

|         |            |                |    | h.      | N Carl   | And I have             | 13             | 4        | E  | н      | H (   | TP.         |

|         |            |                |    |         | ligin de |                        | 14             | L        | 3  | H      | н     | 134         |

|         | AN ST      |                |    |         |          | n an Arian<br>Arthreac | 15             | H        | 4  | 14     | 4     | in prime of |

|         | A Law Mark | and the second |    | True !! | 1.       | Restary.               | and the second |          | X. | 10 9 M | 1. 88 |             |

www.FirstRanker.com

Scanned by CamScanner

## UNIT-6

## **Synchronous and Asynchronous Sequential Circuits**

### 6.1 BASIC DESIGN STEPS

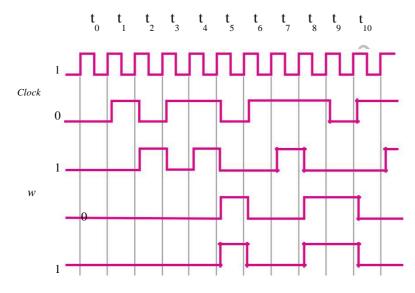

The circuit has one input, w, and one output, z.

All changes in the circuit occur on the positive edge of a clock signal.

The output z is equal to 1 if during two immediately preceding clock cycles the input w was equal to 1. Otherwise, the value of z is equal to 0.

Thus, the circuit detects if two or more consecutive 1s occur on its input *w*. Circuits that detect the occurrence of a particular pattern on its input(s) are referred to as *sequence detectors*.

From this specification it is apparent that the output z cannot depend solely on the present value of w. To illustrate this, consider the sequence of values of the w and z signals during 11 clock cycles, as shown in Figure 8.2. The values of w are assumed arbitrarily; the values of z correspond to our specification. These sequences of input and output values indicate that for a given input value the output may be either 0 or 1. For example, w = 0 during clock cycles  $t_2$  and  $t_5$ , but z = 0 during  $t_2$  and z = 1 during  $t_5$ . Similarly, w = 1during  $t_1$  and  $t_8$ , but z = 0 during  $t_1$  and z = 1 during  $t_8$ . This means that z is not determined only by the present value of w, so there must exist different states in the circuit that determine the value of z.

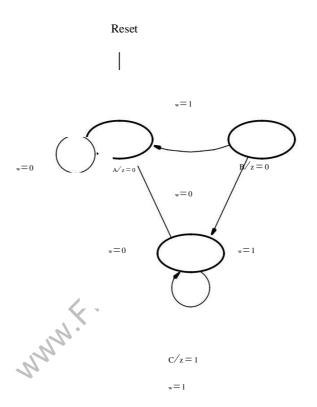

### 6.2 STATE DIAGRAM

The first step in designing a finite state machine is to determine how many states are needed and which transitions are possible from one state to another. There is no set procedure for this task. The designer must think carefully about what the machine has to accomplish. A good way to begin is to select one particular state as a *starting* state; this is the state that the circuit should enter when power is first turned on or when a *reset* signal is applied. For our example let us assume that the starting state is called state *A*. As long as the input *w* is 0, the circuit need not do anything, and so each active clock edge should result in the circuit remaining in state *A*. When *w* becomes equal to 1, the machine should recognize this, and move to a different state, which we will call state *B*. This transition takes place on the next active clock edge **www.FirstRanker.com**

www.FirstRanker.com

after w has become equal to 1. In state B, as in state A, the circuit should keep the value of output z at 0, because it has not yet seen w = 1 for two consecutive clock cycles. When in state B, if w is 0 at the next active clock edge, the circuit should move back to state A. However, if w = 1 when in state B, the circuit should change to a third state, called C, and it should then generate an output z = 1. The circuit should remain in

| Clock cycle: | t0 | t1 | t2 | t3 | t4 | t5 | t6 | t7 | t8 | t9 | t <sub>10</sub> |

|--------------|----|----|----|----|----|----|----|----|----|----|-----------------|

| <i>w</i> :   | 0  | 1  | 0  | 1  | 1  | 0  | 1  | 1  | 1  | 0  | 1               |

| <i>z</i> :   | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 1  | 1  | 0               |

|              |    |    |    |    |    |    |    |    |    |    |                 |

Figure 6.2 Sequences of input and output signals.

state *C* as long as w = 1 and should continue to maintain z = 1. When *w* becomes 0, the machine should move back to state *A*. Since the preceding description handles all possible values of input *w* that the machine can encounter in its various states, we can conclude that three states are needed to implement the desired machine.

Now that we have determined in an informal way the possible transitions between states, we will describe a more formal procedure that can be used to design the corresponding sequential circuit. Behavior of a sequential circuit can be described in several different ways. The conceptually simplest method is to use a pictorial representation in the form of a state diagram, which is a graph that depicts states of the circuit as nodes (circles) and transitions between states as directed arcs. The state diagram in Figure 8.3 defines the behavior that corresponds to our specification. States A, B, and C appear as nodes in the diagram. Node A represents the starting state, and it is also the state that the circuit will reach after an input w = 0 is applied. In this state the output z should be 0, which is indicated as A/z=0 in the node. The circuit should remain in state A as long as w = 0, which is indicated by an arc with a label w = 0 that originates and terminates at this node. The first occurrence of w = 1 (following the condition w = 0) is recorded by moving from state A to state B. This transition is indicated on the graph by an arc originating at A and terminating at B. The label w = 1 on this arc denotes the input value that causes the transition. In state B the output remains at 0, which is indicated as B/z=0 in the node.

cycles, the circuit will remain in state C maintaining z = 1. However, if w becomes 0 when the circuit is either in state B or in state C, the next active clock edge will cause a transition to state A to take place.

In the diagram we indicated that the *Reset* input is used to force the circuit into state A, which is possible regardless of what state the circuit happens to be in. We could treat

Figure 6.3State diagram of a simple sequential circuit

*Reset* as just another input to the circuit, and show a transition from each state to the starting state *A* under control of the input *Reset*. This would complicate the diagram unnecessarily. States in a finite state machine are implemented using flip-flops.

## **6.3 STATE TABLE**

Although the state diagram provides a description of the behavior of a sequential circuit that is easy to understand, to proceed with the implementation of the circuit, it is convenient to translate the information contained in the state diagram into a tabular form. Figure 8.4 shows the *state table* for our sequential circuit. The table indicates all transitions from each *present state* to the *next state* for different values of the input signal. Note that the output z is specified with respect to the present state, namely, the state that the circuit is in at present time. Note also that we did not include the *Reset* input; instead, we made an implicit assumption that the first state in the table is the starting state.

We now show the design steps that will produce the final circuit. To explain the basic design concepts, we first go through a traditional process of manually performing each design step. This is followed by a discussion of automated design techniques that use modern computer aided design (CAD) tools.

## **6.4 STATE ASSIGNMENT**

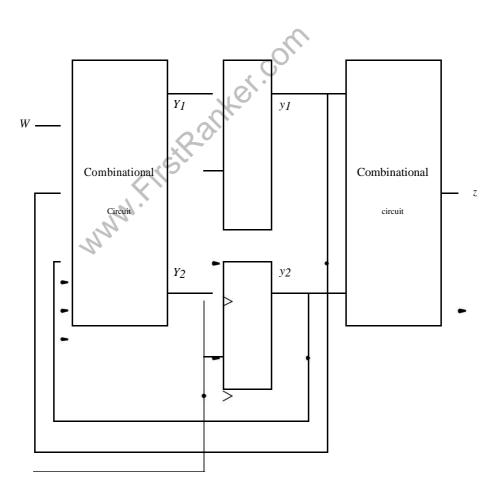

The state table in Figure 8.4 defines the three states in terms of letters A, B, and C. When implemented in a logic circuit, each state is represented by a particular valuation (combi-nation of values) of *state variables*. Each state variable may be implemented in the form of a flip-flop. Since three states have to be realized, it is sufficient to use two state variables. Let these variables be  $y_1$  and  $y_2$ .

Now we can adapt the general block diagram in Figure to our example as shown in Figure 6.5, to indicate the structure of the circuit that implements the required finite state machine. Two flip-flops represent the state variables. In the figure we have not specified the type of flip-flops to be used; this issue is addressed in the next subsection.

| Present | Next         | t state      | Output |

|---------|--------------|--------------|--------|

| state   |              |              | Ζ      |

|         | <i>w</i> = 0 | <i>w</i> = 1 |        |

| А       | А            | В            | 0      |

| В       | А            | С            | 0      |

| С       | А            | С            | 1      |

|         |              |              |        |

State table for the sequential circuit

Clock

The signals  $y_1$  and  $y_2$  are also fed back to the combinational circuit that determines the next state of the FSM. This circuit also uses the primary input signal w. Its outputs are two signals,  $Y_1$  and  $Y_2$ , which are used to set the state of the flip-flops. Each active edge of the clock will cause the flipflops to change their state to the values of  $Y_1$  and  $Y_2$  at that time. Therefore,  $Y_1$  and  $Y_2$  are called the *next-state variables*, and  $y_1$  and  $y_2$  are called the *present-state variables*. We need to design a combinational circuit with inputs w,  $y_1$ , and  $y_2$ , such that for all valuations of these inputs the outputs  $Y_1$  and  $Y_2$  will cause the machine to move to the next state that satisfies our specification. The next step in the design process is to create a truth table that defines this circuit, as well as the circuit that generates z.

www.FirstRanker.com

#### 6.5CHOICE OF FLIP-FLOPS AND DERIVATION OF NEXT-STATE AND OUTPUT EXPRESSIONS

From the state-assigned table in Figure 8.6, we can derive the logic expressions for the next-state and output functions. But first we have to decide on the type of flip-flops that will be used in the circuit. The most straightforward choice is to use D-type flip-flops, because in this case the values of  $Y_1$  and  $Y_2$  are simply clocked into the flip-flops to become the new values of  $y_1$  and  $y_2$ . In other words, if the inputs to the flip-flops are called  $D_1$  and  $D_2$ , then these signals are the same as  $Y_1$  and  $Y_2$ . Note that the diagram in Figure 8.5 corresponds exactly to this use of D-type flip-flops. For other types of flip-flops, such as JK type, the relationship between the next-state variable and inputs to a flip-flop is not as straightforward; we will consider this situation in section 8.7.

The required logic expressions can be derived as shown in Figure 8.7. We use Karnaugh maps to make it easy for the reader to verify the validity of the expressions. Recall that in Figure 8.6 we needed only three of the four possible binary valuations to represent the states. The fourth valuation,  $y_2y_1 = 11$ , should never occur in the circuit because the circuit is constrained to move only within states *A*, *B*, and *C*; therefore, we may choose to treat this valuation as a don't-care condition. The resulting don't-care squares in the Karnaugh maps are denoted by d's. Using the don't cares to simplify the expressions, we obtain

$$Y_1 = wy_1y_2$$

$$Y_2 = w(y_1 + y_2)$$

$$z = y_2$$

Since  $D_1 = Y_1$  and  $D_2 = Y_2$ , the logic circuit that corresponds to the preceding expressions is implemented as shown in Figure 8.8. Observe that a clock signal is included, and the circuit is provided with an active-low reset capability. Connecting the clear input on the flip-flops to an external *Resetn* signal, as shown in the figure, provides a simple means

for forcing the circuit into a known state. If we apply the signal Resetn = 0 to the circuit, then both flip-flops will be cleared to 0, placing the FSM into the state  $y_2y_1 = 00$ .

#### 6.6 TIMING DIAGRAM

we are using positive-edge-triggered flip-flops, all changes in the signals occur shortly after the positive edge of the clock. The amount of delay from the clock edge depends on the propagation delays through the flip-flops. Note that the input signal w is also shown to change slightly after the active edge of the clock. This is a good assumption because in a typical digital system an input such as w would be just an output of another circuit that is synchronized by the same clock.

#### 8.2 STATE-ASSIGNMENT PROBLEM

The basic concepts involved in the design of sequential circuits, we should revisit some details where alternative choices are possible. In section 6.1 we suggested that some state assignments may be better than others. To illustrate this we can reconsider the example in Figure 8.4. We already know that the state assignment in Figure 6.6 leads to a simple-looking circuit in Figure 8.8. But can the FSM of Figure 6.4 be implemented with an even simpler circuit by using a different state assignment.

In general, circuits are much larger than our example, and different state assignments can have a substantial effect on the cost of the final implementation. While highly desirable, it is often impossible to find the best state assignment for a large circuit. The exhaustive approach of trying all possible state assignments is not practical because the number of available state assignments is huge. CAD tools usually perform the state assignment using heuristic techniques. These techniques are usually proprietary, and their details are seldom published.

#### 6.8 ONE-HOT ENCODING

Another interesting possibility is to use as many state variables as there are states in a sequential circuit. In this method, for each state all but one of the state variables are equal to 0. The variable whose value is 1 is deemed to be "hot." The approach is known as the *one-hot encoding* method.

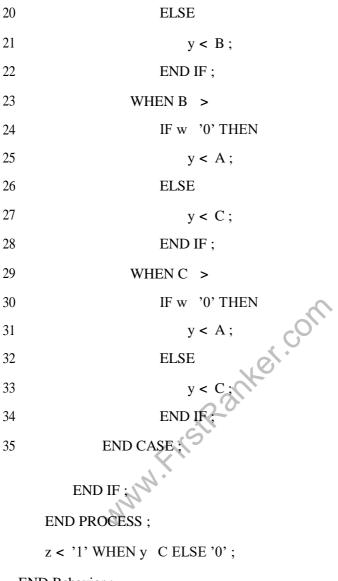

#### 6.9 VHDL CODE FOR MOORE-TYPE FSMS

VHDL does not define a standard way of describing a finite state machine. Hence while adhering to the required VHDL syntax, there is more than one way to describe a given FSM. An example of VHDL code for the FSM of Figure 8.3 is given in Figure 8.29. For the convenience of discussion, the lines of code are numbered on the left side. Lines 1 to 6 declare an entity named *simple*, which has input ports *Clock*, *Resetn*, and *w*, and output port *z*. In line 7 we have used the name *Behavior* for the architecture body, but of course, any valid VHDL name could be used instead.

The TYPE keyword, which is a feature of VHDL that we have not used previously. The TYPE keyword allows us to create a user-defined signal type. The new signal type is named State\_type, and the code specifies that a signal of this type can have three possible values: A, B, or C. Line 9 defines a signal named y that is of the State\_type type. The y signal is used in the architecture body to represent the outputs of the flip-flops that implement the states in the FSM. The code does not specify the number of bits represented by y. Instead, it specifies that y can have the three symbolic values A, B, and C. This means that we have not specified the number of state flip-flops that should be used for the FSM. As we will see below, the VHDL compiler automatically chooses an appropriate number of state flip-flops when synthesizing a circuit to implement the machine. It also chooses the state assignment for states A, B, and C. Some CAD systems, such as Quartus II, assume that the first state listed in the TYPE statement (line 8) is the reset state for the machine. The state assignment that has all flip-flop outputs equal to 0 is used for this state. Later in this section, we will show

www.FirstRanker.com

#### DESIGN OF FINITE STATE MACHINES USING CAD TOOLS

509

LIBRARY ieee; USE ieee.std logic 1164.all; **ENTITY** simple IS PORT (Clock, Resetn, 4 : IN STD LOGIC ; W STD LOGIC) Ζ 5 : OUT; \_ ARCHITECTURE Behavior OF simple IS SIGNAL y : State type ; BEGIN PROCESS (Resetn, Clock) BEGIN IF Resetn '0' THEN 14 y < A;ELSIF (Clock'EVENT AND Clock '1') 15 THEN 16 CASE y IS 17 WHEN A > 18 IF w '0' THEN 19 y < A;

www.FirstRanker.com

END Behavior;

### 6.9 SPECIFYING THE STATE ASSIGNMENT IN VHDL CODE

That the state assignment may have an impact on the complexity of the designed circuit. An obvious objective of the state-assignment process is to minimize the cost of implementation. The cost function that should be optimized may be simply the number of gates and flip-flops. But it could also be based on other considerations that may be representative of the structure of PLD chips used to implement the design. For example, the CAD software may try to find state

encodings that minimize the total number of AND terms needed in the resulting circuit when the target chip is a CPLD.

In VHDL code it is possible to specify the state assignment that should be used, but there is no standardized way of doing so. Hence while adhering to VHDL syntax, each CAD system permits a slightly different method of specifying the state assignment. The Quartus II system recommends that state assignment be done by using the attribute feature of VHDL. An *attribute* refers to some type of information about an object in VHDL code. All signals automatically have a number of associated *predefined* attributes. An example is the EVENT attribute that we use to specify a clock edge, as in Clock'EVENT.

In addition to the predefined attributes, it is possible to create a user-defined attribute. The *user-defined* attribute can be used to associate some desired type of information with an object in VHDL code. In Quartus II manual state assignment can be done by creating a user-defined attribute associated with the State\_type type. This is illustrated in Figure 8.34, which shows the first few lines of the architecture from Figure 8.33 with the addition of a user-defined attribute. We first define the new attribute called ENUM\_ENCODING, which has the type STRING. The next line associates ENUM\_ENCODING with the State\_type type and specifies that the attribute has the value "00 01 11". When translating the VHDL code, the Quartus II compiler uses the value of ENUM\_ENCODING to make the state assignment A = 00, B = 01, and C = 11.

ARCHITECTURE Behavior OF simple IS

| TYPE State TYPE IS (A, B, C); | TYPE | State | TYPE | IS (A, | Β, | C) | ; |

|-------------------------------|------|-------|------|--------|----|----|---|

|-------------------------------|------|-------|------|--------|----|----|---|

ATTRIBUTE ENUM ENCODING

: STRING ;

ATTRIBUTE ENUM ENCODING OF State type : TYPE IS "00 01 11";

SIGNAL y present, y next

: State type ;

BEGIN

www.FirstRanker.com

**Figure 8.34** A user-defined attribute for manual state assignment.

;

www.FirstRanker.com

LIBRARY ieee; USE ieee.std logic 1164.all **ENTITY** simple IS PORT (Clock, Resetn, : INSTD LOGIC ; W : OUT STD LOGIC) Ζ ; END simple ; ARCHITECTURE Behavior OF simple IS SIGNAL y presentz, y next : STD LOGIC VECTOR(1 DOWNTO 0); CONSTANT A : STD LOGIC VECTOR(1 DOWNTO 0) : "00"; CONSTANT B : STD LOGIC VECTOR(1 DOWNTO 0) : "01"; CONSTANT C : STD LOGIC VECTOR(1 DOWNTO 0) : "11"; BEGIN PROCESS ( w, y present )

BEGIN

CASE y present IS

WHEN A >

IF w '0' THEN y next < A;

IF Resetn

y present <

www.FirstRanker.com

www.FirstRanker.com

```

ELSE y next < B;

-

END IF;

WHEN B >

IF w '0' THEN y next < A;

ELSE y next < C ;

_

END IF;

WHEN C >

IF w '0' THEN y next < A;

ELSE y next < C;

END IF

WHEN OTHERS >

next < A;

END CASE ;

END PROCESS ;

PROCESS (Clock, Resetn)

BEGIN

'0'

THEN

Α;

```

ELSIF (Clock'EVENT AND Clock '1') THEN

www.FirstRanker.com

y present < y next ;

END IF;

END PROCESS ;

z < '1' WHEN y present C ELSE '0';

END Behavior;

### 6.10 SPECIFICATION OF MEALY FSMS USING VHDL

A Mealy-type FSM can be specified in a similar manner as a Moore-type FSM. Figure 8.36 gives complete VHDL code for the FSM in Figure 8.23. The state transitions are described in the same way as in our original VHDL example in Figure 8.29. The signal y represents the state flip-flops, and State\_type specifies that y can have the values A and B. Compared to the code in Figure 8.29, the major difference in the case of a Mealy-type FSM is the way in which the code for the output is written. In Figure 8.36 the output z is defined using a CASE statement. It states that when the FSM is in state A, z should be 0, but when in state B, z should take the value of w. This CASE statement properly describes the logic needed for z, but it may not be obvious why we have used a second CASE statement in the code, rather than specify the value of z inside the CASE statement that defines the state transitions. The reason is that the CASE statement for the state transitions is nested inside the IF statement that waits for a clock edge to occur. Hence if we placed the code for z inside this CASE statement, then the value of z could change only as a result of a clock edge. This does not meet the requirements of the Mealy-type FSM, because the value of z must depend not only on the state of the machine but also on the input w.

Implementing the FSM specified in Figure 8.36 in a CPLD chip yields the same equa-tions as we derived manually in section 8.3. Simulation results for the synthesized circuit appear in Figure 8.37. The input waveform for w is the same as the one we used for the Moore-type machine in Figure 8.32. Our Mealy-type machine behaves correctly, with z becoming 1 just after the start of the second consecutive clock cycle in which w is 1.

In the simulation results we have given in this section, all changes in the input w occur immediately following a positive clock edge. This is based on the assumption stated in section 8.1.5 that in a real circuit w would be synchronized with respect to the clock that controls the FSM. In Figure 8.38 we illustrate a problem that may arise if w does not meet this specification. In this case we have assumed that the changes in w take place at the

www.FirstRanker.com

LIBRARY ieee; USE ieee.std logic 1164.all ; ENTITY mealy IS PORT (Clock, Resetn, : INSTD LOGIC ; W : OUT STD LOGIC) Ζ ; END mealy; ARCHITECTURE Behavior OF mealy IS TYPE State type IS (A, B) SIGNAL y : State type ; BEGIN PROCESS (Resetn, Clock) 2 BEGIN IF Resetn '0' THEN y < A; ELSIF (Clock'EVENT AND Clock '1') THEN CASE y IS WHEN A >

IF w '0' THEN y < A;

www.FirstRanker.com

ELSE y < B;

END IF;

WHEN B >

IF w '0' THEN y < A;

ELSE y < B;

END IF;

END CASE ;

END Behavior;