# **Pulse & Digital Circuits**

### **CONTENTS**

| S.NO | NAME OF THE TOPIC                      | Page.no |

|------|----------------------------------------|---------|

| 1.   | Linear Wave Shaping                    | 3       |

| 2.   | Non-Linear Wave Shaping                | 35      |

| 3.   | Multi vibrators                        | 61      |

| 4.   | Sweep Circuits                         | 89      |

| 5.   | Synchronization and frequency division | 118     |

| 6.   | Logic Gates                            | 130     |

| 7.   | Blocking Oscillator                    | 147     |

|      | www.FirstPe                            |         |

## **Pulse & Digital Circuits**

### 1. Linear Wave Shaping

### **SYLLABUS:**

High Pass and Low Pass RC Circuits and their Response for Sinusoidal, Step Voltage, Pulse, Square Wave and Ramp Inputs. High Pass RC Circuit as a Differentiator. Low Pass RC Circuit as an Integrator. Attenuators and their application as CRO Probe. RL and RLC Circuits and their response for step input. Ringing circuit.

#### Linear wave shaping:

#### Introduction:

If a circuit is designed with components like R, L and C then it is called linear circuit. When sinusoidal signal is applied, the shape of the signal is preserved at the output with or without change in the amplitude and shape. But a non-sinusoidal signal alters the output when it is transmitted through a linear circuit. The process whereby the form of nonsinusoidal signals such as step, pulse, square wave, ramp and exponential is altered by transmission through a linear network is called linear wave shaping.

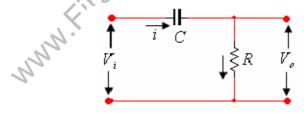

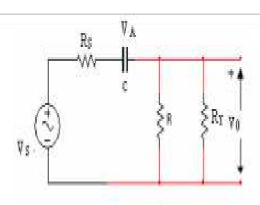

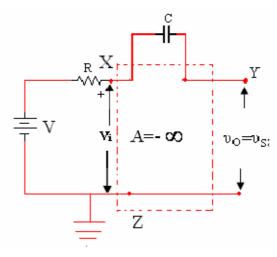

### 1.1 High pass RC circuit:

Consider high pass RC circuit as shown in fig.1 below.

#### Fig.1 highpass rc circuit

The capacitor offers high reactance at low frequency and low reactance at high frequency. Hence low frequency components are not transmitted, but high frequencies are with less attenuation. Therefore the output is large and the circuit is called a high pass circuit.

Let us see now is, what will be the response if different types of inputs, such as, sinusoidal ,step, pulse, square wave, exponential and ramp are applied to a high pass circuit.

## **Pulse & Digital Circuits**

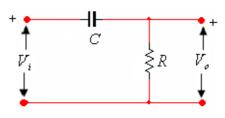

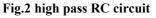

### 1.2 Response of high pass RC for sinusoidal input:

#### (i) sinusoidal input:

First consider the response of a high pass RC circuit.

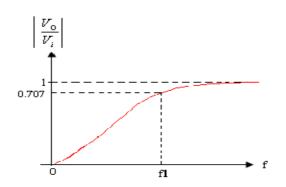

Hence, f1 is the lower cut -off frequency of the highpass circuit.

## **Pulse & Digital Circuits**

Fig.3 frequency response curve for sinusoidal input.

### 1.3 High Pass RC response for Step signal input.

#### (ii) Step input

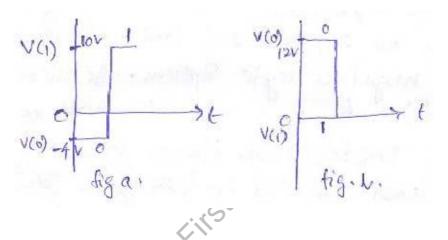

A Step voltage is defined as,  $V_i = 0$  for t < 0  $V_i = V$  for t<sup>3</sup> 0 and www.First V Π

**Fig.4 Step Voltage**

The output voltage is of the form

$V_{o} = B_1 + B_2 e^{-t/\tau}$

Where  $\tau = RC$ , the time constant of the circuit.

B1 is the steady state value as  $t \rightarrow \infty$ , and hence  $o V \rightarrow B1$

Let the final value be which we denote as  $V_{f}$ .

Then  $V_f = B1$ .

## **Pulse & Digital Circuits**

B2 is determined by the initial output voltage. At t = 0,  $V_i = V_o = B1 + B2$ Therefore,  $B2 = V_i - B1$  $= V_i - V_f$ Hence the general solution is

$V_o = V_f + (V_i - V_f) e^{-t/t}$

**Fall time**  $t_f$ : When a step is applied, the time taken for the output voltage to fall from 90  $\Box$  of its initial value to 10% of its initial value is the fall time. It indicates how fast the output reaches its steady state value.

The output voltage at any instant of time, in high pass circuit, is given by

$$V_{o}(t) = Ve^{-t/\tau}, \quad \text{At } t = t_{1}, \quad V_{o}(t_{1}) = 90\% \text{ of } V = 0.9V$$

$$0.9 = e^{-t/\tau}$$

$$e^{t/\tau} = 1/0.9 = 1.11$$

$$t_{1}/\tau = \ln(1.11)$$

$$t_{1} = \tau \ln(1.11) = 0.1 \tau$$

$$At \ t = t_{2}, \quad V_{o}(t) = 10\% \text{ of } V = 0.1V$$

$$0.1 = e^{-t^{2}/\tau}$$

$$e^{t^{2}/\tau} = 1/0.1 = 10$$

$$t_{2} = \tau \ln(10) = 2.3 \tau$$

fall time,  $t_f$  = t2- t1 = 2.3  $\tau$ - 0.1  $\tau$ = 2.2  $\tau$

The lower half power frequency of the highpass circuit is

$$f_{1} = \frac{1}{2\pi RC}$$

$$\tau = RC = \frac{1}{2\pi f_{1}}$$

# **Pulse & Digital Circuits**

Fall time =

$$t_f = 2.2 \tau = \frac{2.2}{2\pi f_1} = \frac{0.35}{f_1}$$

Hence, the fall time is inversely proportional to f1, the lower cut-off frequency.

### 1.4 High Pass RC response for Square signal input.

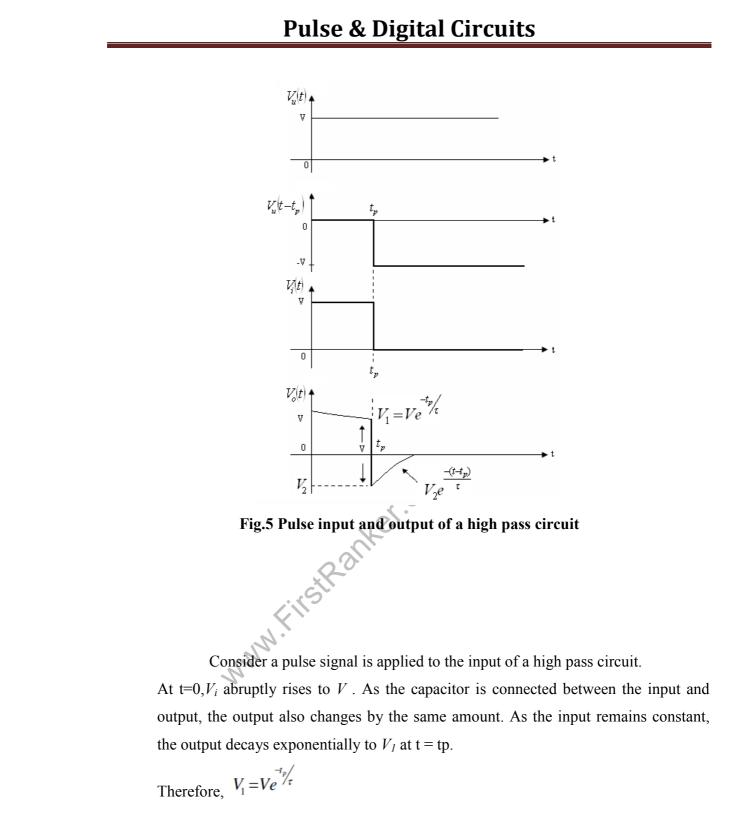

(iii)**Pulse input:** A pulse can be expresseds combination of a positive (negative) step followed by negative(positive) step w.r.t. times i.e. $V_i$  = Vu (t) - Vu (t – tp) where tp is the duration of the pulse as shown below in fig.5

At  $t = t_p$ , the input abruptly falls by *V*.*V o* also falls by the same amount.

At  $t = t_p$ ,  $V o = V_1 - V$

# **Pulse & Digital Circuits**

Since V1 is less than V, V o is negative and its value is V2 and this decays to zero exponentially.

For t > tp,

$$V_o = (V_1 - V_1) e^{-(l - t_p)/2}$$

But

$$V_1 = V e^{-t_p/\tau}$$

$$\therefore V_p = V (e^{-t_p/\tau} - 1) e^{-(t-t_p)/\tau}$$

The response of a high pass circuit with pulse input for different values of  $\tau$  is plotted in fig.1.6.

Fig.6 Response of a high pass circuit for pulse input

It is very clear that output has distortion when a pulse is passing through a high pass RC circuit. The shape of the pulse at the output is almost preserved when the time constant  $\Box$

## **Pulse & Digital Circuits**

is very large (fig.6b) whereas in fig.6c there is a tilt at the top of the pulse and an undershoot at the end of the pulse.

If  $\tau \ll t_p$  (fig.1.6d), the output consists of a positive spike at the beginning of the pulse and a negative spike at the end of the pulse, that means a highpass circuit converts a pulse into spikes called 'peaking'. To have a less distortion,  $\tau$  must be very much larger than the time period of the input pulse. In general, there is an undershoot at the end of the pulse. The area above the axis (A1) is always equal to the area below (A2).

### Area A1:

0< t< t<sub>p</sub>

$$A_{1} = \left[ -V\tau e^{\frac{-t_{p}}{\tau}} + V\tau \right] = V\tau (1 - e^{\frac{-t_{p}}{\tau}})$$

$$A_{2} = \int_{t_{p}}^{\infty} V(e^{-t_{p}/\tau} - 1)e^{-(t-t_{p})/\tau} dt$$

# **Pulse & Digital Circuits**

$$= \int_{t_p}^{\infty} \left[ V e^{-t/\tau} - V e^{-(t-t_p)/\tau} \right] dt$$

$$= \left[ \frac{V e^{-t/\tau}}{-1/\tau} \right]_{t_p}^{\infty} - \left[ V \frac{1}{-1/\tau} e^{-(t-t_p)/\tau} \right]_{t_p}^{\infty}$$

$$A_2 = \left[ V \tau e^{-t_p/\tau} - V \tau \right] = -V \tau (1 - e^{-t_p/\tau})$$

$$|A_1| = |A_2|$$

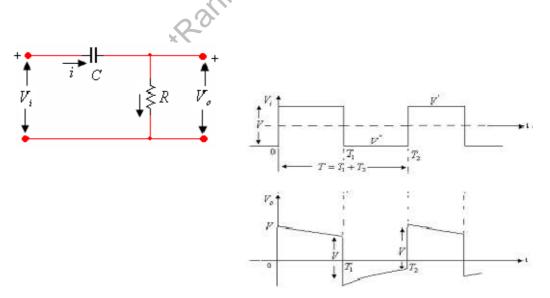

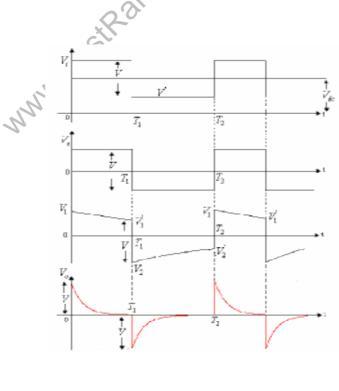

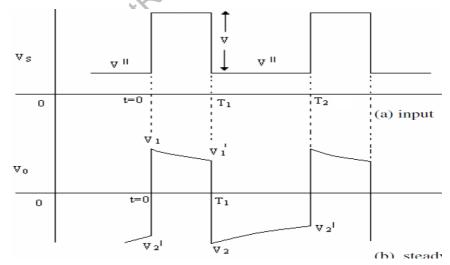

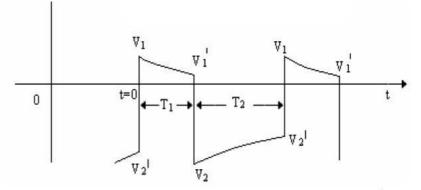

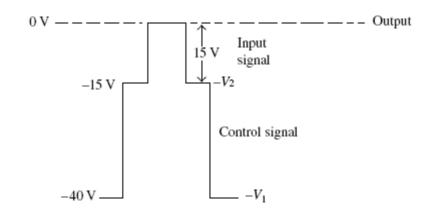

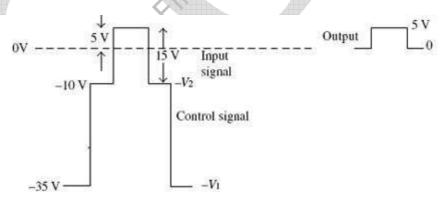

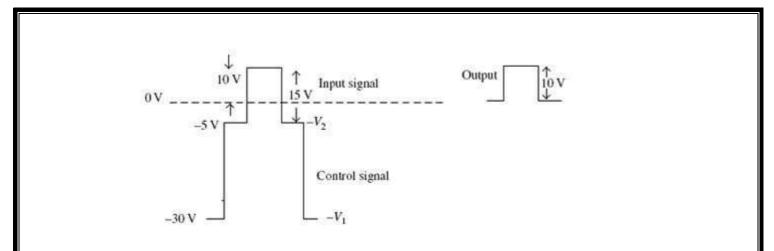

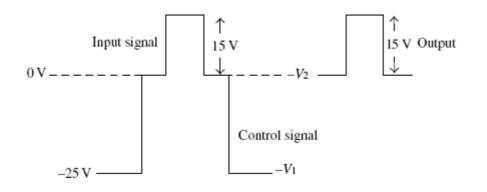

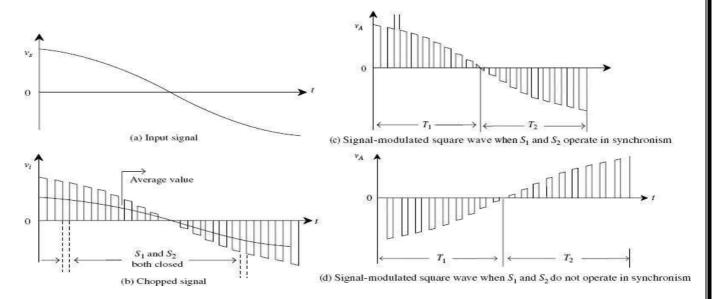

### (iv) Square wave-Average level

A waveform that has a constant amplitude ' V for a time T1 and has another constant Amplitude ' V for a time T2 and which is repetitive with a time T= (T1+ T2) is called a square Wave. If T1= T2 =T/2, then it is called a symmetric square wave and the typical input-output

Waveforms of the high pass circuit are shown in fig below.

Fig.8 output of a high pass for symmetric square wave input

## **Pulse & Digital Circuits**

Whatever is the dc component associated with the periodic input, waveform the dc level of the Steady state output signal for the high pass circuit is always zero.

This can be verified by using KVL equation

$$V_i = \frac{q}{C} + V_o$$

where q is the capacitor charge Differentiating with respect to t

$$\frac{dV_i}{dt} = \frac{1}{C}\frac{dq}{dt} + \frac{dV_o}{dt}$$

But i =  $\frac{dq}{dt}$

Substituting above condition

$$\frac{dVi}{dt} = \frac{i}{C} + \frac{dV_o}{dt}$$

con

since  $V_o = iR$ ,  $i = \frac{V_o}{R}$  and  $RC = \tau$

Multiplying by dt and integrating over the time period T we get

$$\therefore \frac{dV_i}{dt} = \frac{V_o}{\tau} + \frac{dV_o}{dt}$$

Multiplying by dt and integrating over the time period T we get

$$\int_0^T dV_i = [V_i]_0^T = V_i(T) - V_i(0)$$

$$\int_0^T \frac{V_o}{\tau} dt = \frac{1}{\tau} \int_0^T V_o dt$$

$$\int_0^T dV_o = [V_o]_0^T = V_o(T) - V_o(0)$$

From above equations

# **Pulse & Digital Circuits**

$$V_{i}(T) - V_{i}(0) = \frac{1}{\tau} \int_{0}^{T} V_{o} dt + \left[ V_{o}(T) - V_{o}(0) \right]$$

Under steady-state conditions, the output and the input waveform are repetitive with a time period T. Therefore,

$$\int_{0}^{T} V_{o} dt = 0 \qquad V_{i}(T) = V_{o}(T) \text{ and } V_{i}(0) = V_{o}(0)$$

Since this integral represents the area under the output waveform over one cycle, it is evident that the dc in the steady state is always zero.

### 1.5 High pass RC response for Square wave input:

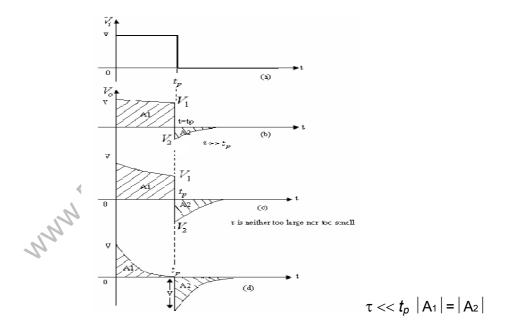

Now consider the response of the high pass RC circuit for a square wave input for different values of the time constant,  $\tau$ , fig below.

13

www.FirstRanker.com

# **Pulse & Digital Circuits**

#### Fig.9 Response of a highpass circuit for square input

- a) Square Wave input

- (b) Response  $\tau \gg T1$  and  $\tau \gg T2$

- (c) Response when  $\tau$  is neither too large nor too small

- (d) Response when  $\tau$  is very small

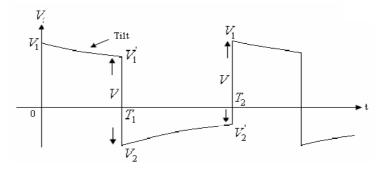

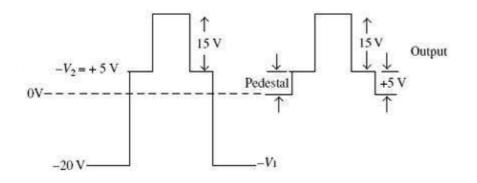

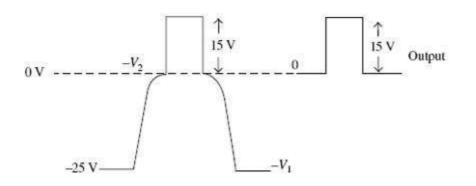

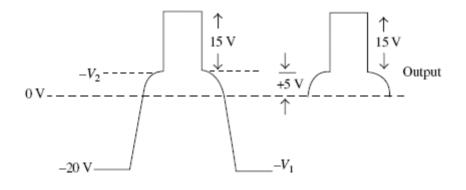

Consider the typical response of the highpass circuit for square wave input, fig.10

Fig.10 response of a highpass RC circuit for squarewave input

We know that  $V_1 = V_1 e^{-T_1/T}$  and  $V_1 - V_2 = V$ And  $V_2 = V_2 e^{-T_1/T}$  and  $V_1 - V_2 = V_1$ For a symmetric square wave  $T_1 = T_2 = \frac{T}{2}$ And because of symmetry'  $V_1 = -V_2$  and  $V_1 = -V_2'$ 'From equation  $V_1 - V_2 = V$ But  $V_1 = -V_1 e^{-T_1/T}$ Therefore  $-T_1/T$

$$V_1 e^{-T_1/\tau} - V_2 = V$$

www.FirstRanker.com

# **Pulse & Digital Circuits**

From

$$V_1 = -V_2$$

Substituting, we have

$$V_{1}e^{-\frac{T}{T}} + V_{1} = V$$

$$V_{1}(1 + e^{-\frac{T}{T}}) = V$$

Thus,

$$V_{1} = \frac{V}{1 + e^{-\frac{T}{T}}}$$

For a symmetric squarewave as  $T_1 = T_2 = \frac{T}{2}$ ,

Therefore

$$V_{1} = \frac{V}{1 + e^{-T/2\tau}}$$

But,  $V_{1}' = V_{1} e^{-T/2\tau}$

$V_{1}' = V \frac{e^{-T/2\tau}}{(1 + e^{-T/2\tau})}$

There is a tilt in the output waveform. The percentage tilt is defined as

% Tilt = P =

$$\frac{\frac{V_1 - V_1}{V/2}}{\frac{V/2}{1 + e^{-T/2\tau}}} \times 100\%$$

=  $\frac{\frac{V}{1 + e^{-T/2\tau}} - \frac{Ve^{-T/2\tau}}{1 + e^{-T/2\tau}}}{\frac{V/2}{2}} \times 100\%$

## **Pulse & Digital Circuits**

If

$$\frac{T}{2\tau} \ll 1$$

P  $\approx \frac{T}{2\tau} \times 100\%$  since  $\frac{T}{2t} \ll 1$

P  $= \frac{T}{2\tau} \times 100\%$ , for a symmetrical squarewave

The lower cut-off frequency,  $f_1 = \frac{1}{2\pi\tau}$

Therefore  $\frac{1}{2\tau} = \pi f_1$

P  $= \pi f_1 T \times 100\%$

Therefore,  $P = \frac{\pi f_1}{f} \times 100\%$ , since  $T = \frac{1}{f}$

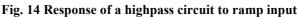

### 1.6 High Pass RC response for Ramp signal input.

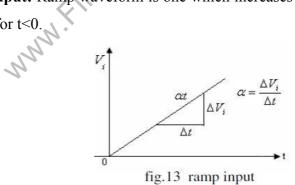

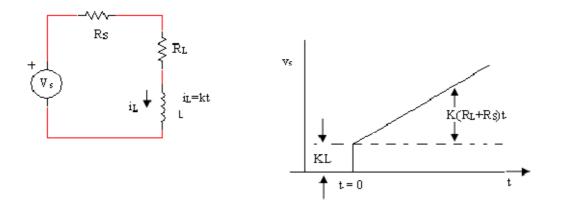

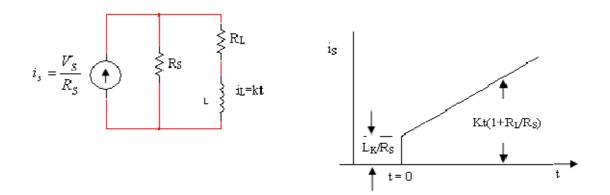

(v) Ramp input: Ramp waveform is one which increases linearly with time for t> 0 and is zero for t<0.</li>

Let the input to the high pass circuit be  $V_i = \alpha t$  where  $\alpha$  is the slope fig.13

www.FirstRanker.com

## **Pulse & Digital Circuits**

• t

Transmission error is defined as the deviation from linearity and is given by

$$e_{t} = \frac{V_{i} - V_{o}}{V_{i}}$$

$$V_{i} = \alpha t$$

# **Pulse & Digital Circuits**

At

$$t = T$$

,  $V_i = \alpha T$ , And  $V_o = \alpha T \left(1 - \frac{T}{2\tau}\right)$

Therefore  $e_t = \frac{\alpha T - \alpha T (1 - \frac{T}{2\tau})}{\alpha T} = \frac{\alpha T^2}{\alpha T} = \frac{T}{2\tau}$

Thus,  $e_t = \frac{T}{2\tau} = \prod f_1 T \ as \frac{1}{2\tau} = \pi f_1$

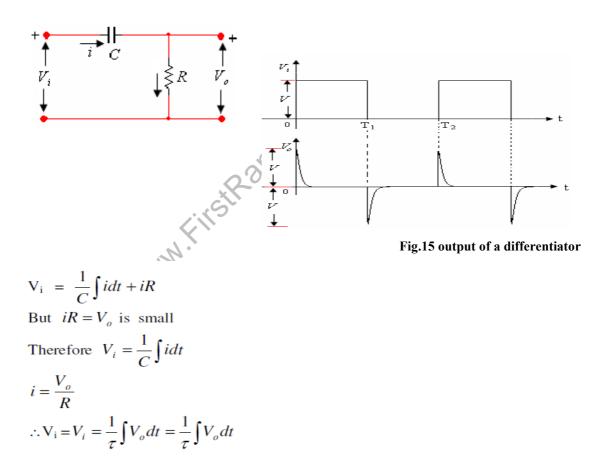

### 1.7 HighPass RC Circuit as Differentiator

If the time constant of the RC highpass circuit is very much smaller than the time period of the input signal, then the circuit behaves as a differentiator. Then the voltage drop across R is very small when compared to the drop across C.

# **Pulse & Digital Circuits**

Differentiating

$$\frac{dV_i}{dt} = \frac{V_o}{\tau}$$

$$V_o = \tau \frac{dV_i}{dt}$$

$$\therefore V_o \propto \frac{dV_i}{dt}$$

The output is proportional to the differential of the input signal.

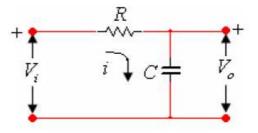

### **LOWPASS CIRCUITS:**

#### Introduction:

Low pass circuit is one which allows low frequencies with less attenuation and high frequencies with maximum attenuation. This is because capacitance offers high reactance at low frequencies and hence there is an output.

ankercom

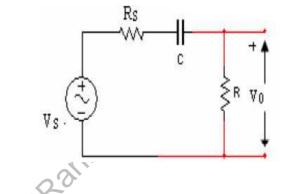

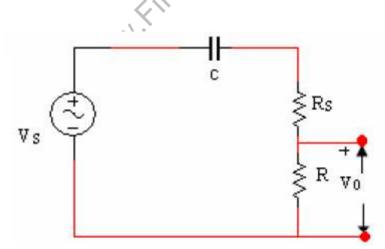

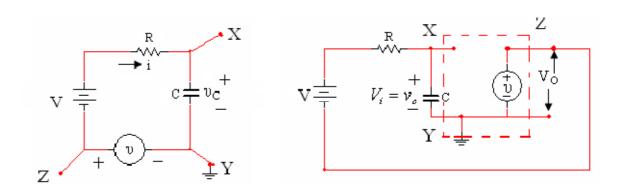

1.8 LOWPASS RC CIRCUIT: Following is the low pass RC circuit.

Fig.16 Low pass RC Circuit

# **Pulse & Digital Circuits**

At low frequencies the reactance of C is large and as frequency increases its Reactance decreases. Hence the output is larger for smaller frequencies and is smaller for larger frequencies. Hence this circuit is called a low pass circuit.

Consider the response of this circuit for different types of inputs.

### 1.9 Low Pass RC response for Sine signal input.

**i) SINUSOIDAL INPUT:** For the circuit shown above, if sinusoidal signal is applied as an input, the output Vo is given by

$$V_a = V_i \frac{\frac{1}{j\omega C}}{R + \frac{1}{j\omega C}}$$

$$\frac{V_o}{V_i} = \frac{1}{1 + j\omega CR}$$

$$\frac{\left|\frac{V_o}{V_i}\right| = \frac{1}{\sqrt{1 + (\omega CR)^2}} = \frac{1}{\sqrt{1 + \left(\frac{\omega}{\omega_2}\right)^2}}, \text{ where } \omega_2 = \frac{1}{CR}$$

At  $\omega = \omega_2$ ,  $\left|\frac{V_o}{V_i}\right| = \frac{1}{\sqrt{2}} = 0.707$

Hence, f2 is the upper cut-off frequency as shown in the response curve below.

Fig.17 Response of low pass circuit to sinusoidal input

**1.10 Low Pass RC response for Step signal input.**

20

# **Pulse & Digital Circuits**

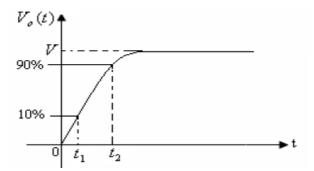

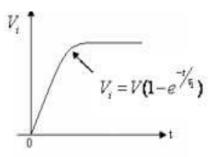

(ii) **STEP INPUT:** When a step voltage is applied as input to the lowpass circuit the output will be appeared as shown in fig. below.

Fig.18 Response of lowpass circuit to step input

ercom

$$V_o = V_f + \left(V_i - V_f\right)e^{\frac{-t}{\tau}}$$

Here,  $V_f = V$  and  $V_i = 0$

$$\therefore V_o(t) = V - Ve^{\frac{-t}{\tau}} = V\left(1 - e^{\frac{-t}{\tau}}\right)$$

As  $t \to \infty$ ,  $V_o(t) \to V$

On the other hand, the output can be obtained by solving the differential equation.

www.FirstRanker.com

# **Pulse & Digital Circuits**

$$V = V_{i} = Ri + \frac{1}{C} \int i dt$$

We know that  $\frac{1}{C} \int i dt = V_{o}$

$\frac{i}{C} = \frac{dV_{o}}{dt}$

$i = C \frac{dV_{o}}{dt}$

$V = RC \frac{dV_{o}}{dt} + V_{o}$

$V = \tau \frac{dV_{o}}{dt} + V_{o}$  Solving for

**Rise time:** The time taken for the output to reach from 10% of its final value to 90% of its final value is called rise time. From equation

$V_o(t) = V_o = V - Ve^{\frac{-t}{\tau}} = V\left(1 - e^{\frac{-t}{\tau}}\right)$

$$0.9 = 1 - e^{\frac{-t}{\tau}}$$

$$e^{-t_2/\tau} = 0.1$$

$$t_2 = 2.3\tau$$

Rise time  $t_r = t_2 - t_1 = 2.3 \tau - 0.1 \tau = 2.2 \tau$

Also  $f_2 = \frac{1}{2\pi RC}$

$$RC = \tau = \frac{1}{2\pi f_2}$$

# **Pulse & Digital Circuits**

### 1.11Low pass RC response for pulse input:

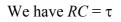

Let the input of low pass rc is a pulse signal with pulse width T the response of low pass RC for pulse input under different conditions will be as follows.

Fig.20 Response of low pass RC for pulse input under different conditions

# **Pulse & Digital Circuits**

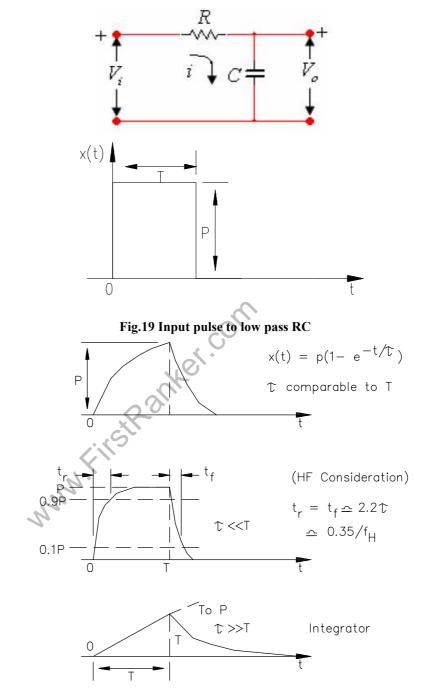

### 1.12 Response of low pass RC for square input:

The shape of the output waveform of an RC low-pass circuit depends upon the value of the circuit time constant T (as compared to pulse duration  $t_p$ ). For a pulse waveform of the low-pass circuit may be short, long or medium as compared to  $t_p$ , the pulse duration of the input pulse wave. The output wave form for three different conditions for square wave input will be as follows .The conditions are T<<  $t_p$ , T= $t_p$ , T>> $t_p$ .

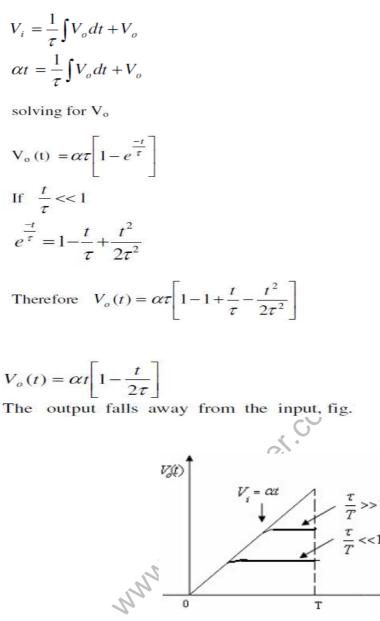

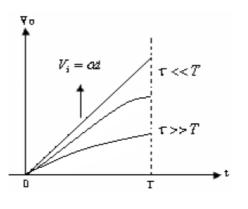

### **1.13 Response of Low pass circuit for ramp input:**

When a ramp is applied as input to a lowpass circuit, the output deviates from the input which is defined as transmission error et. Mathematically it can be written as

# **Pulse & Digital Circuits**

The input is a ramp i.e.  $V_i = \alpha t$

100 10

We have

$$V_i = \tau \frac{dV_0}{dt} + V_0$$

$\therefore \alpha t = \tau \frac{dV_0}{dt} + V_0$

solving for output, we have

$$V_{o}(t) = -\alpha \tau + \alpha t + \alpha \pi e^{-t/\tau}$$

$$V_{o}(t) = \alpha \left[ t - \tau \left( 1 - e^{-t/\tau} \right) \right]$$

At  $t = T$

$$V_{o}(T) = \alpha \left[ T - \tau \left( 1 - e^{-T/\tau} \right) \right]$$

Case 1: If  $\tau \ll T$ , then the deviation of the output from the input is very small since

$$e^{-T/\tau} \approx 0$$

$V_o(t) = \alpha(T - \tau)$

**Case 2:** If  $\tau \gg T$ , then  $e^{-T/\tau}$  can be expanded as series

$$V_o(t) = \alpha \left[ T - \tau \left( \frac{T}{\tau} - \frac{T^2}{2\tau^2} \right) \right]$$

$$= \alpha \left[ T - T + \frac{T^2}{2\tau} \right] = \frac{\alpha T^2}{2\tau} - \dots - \dots 2.36$$

The response is plotted in fig. below

2

25

## **Pulse & Digital Circuits**

$$e_{t} = \frac{V_{i} - V_{0}}{V_{i}}$$

$$= \frac{\alpha T - \alpha (T - \tau)}{\alpha T}$$

$$e_{t} = \frac{\tau}{T}$$

$$f_{2} = \frac{1}{2\pi\tau}$$

$$\tau = \frac{1}{2\pi\tau}$$

### 1.14 Low pass circuit as an integrator

For the low pass circuit to behave as an integrator  $\tau \gg T$  then the voltage Variation in C is very small

$$\begin{split} i &= \frac{V_i}{R} \\ \text{Therefore} \quad V_o &= \frac{1}{C} \int i dt = \frac{1}{RC} \int V_i dt = \frac{1}{\tau} \int V_i dt \end{split}$$

The output is proportional to the integral of the input signal.

Hence a low pass circuit with large time constant produces an output that is proportional to the integral of the input.

## **Pulse & Digital Circuits**

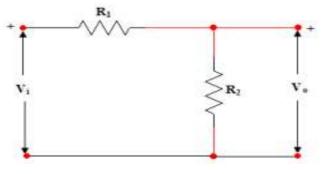

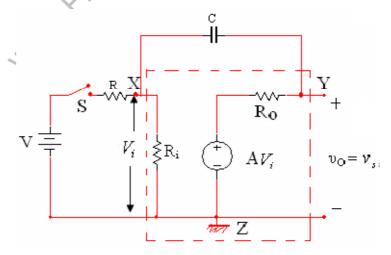

### 1.15 Attenuators:

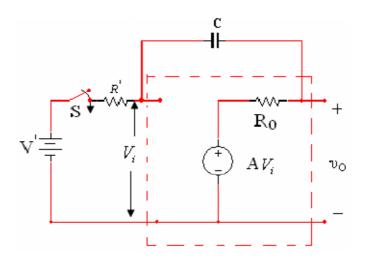

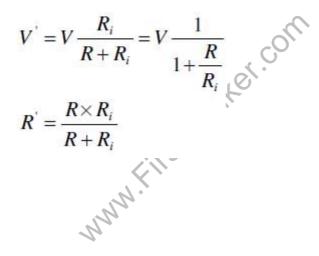

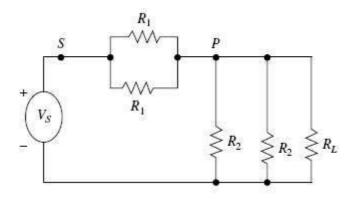

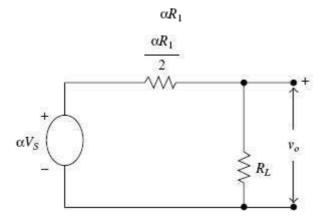

An attenuator is a circuit that reduces the amplitude of the signal by a finite amount. A simple resistance attenuator is as shown below.

Fig.22 Resistive Attenuator

The output is reduced depending on the choice of R1 and R2. The output of this attenuator can be connected as input to an amplifier having a stray capacitance C2 and input resistance Ri.If Ri>>R2, then the effective value of resistance will be smaller than R2. The attenuator circuit will be now as

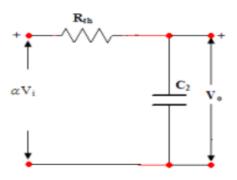

Reducing the two loop network into a single loop network by Thevenizing

$$V_{Tk} = V_i \times \frac{R_2}{R_1 + R_2} = \alpha V_i$$

where  $\alpha = \frac{R_2}{R_1 + R_2}$

and

$$R_{ik} = R_1 //R_2$$

Hence the above circuit reduces to

## **Pulse & Digital Circuits**

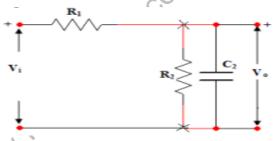

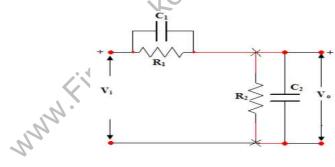

When the input  $\alpha$ Vi is applied to this low pass RC circuit, the output will not reach the steady-state value instantaneously. For e.g. in the above circuit, R1=R2=1M and C2 = 20nF.Then the rise time t<sub>r</sub> = 2.2RthC2=2.2×0.5×10<sup>6</sup>×20×10<sup>-9</sup>,tr = 22msec. which says that approximately after a time interval of 22 msec. after the application of the input  $\alpha$ Vi to the circuit, the output reaches the steady state value. Obviously this is an abnormally long time delay. An attenuator of this type is called an uncompensated attenuator and the response is depending on frequency. To make the response of the attenuator independent of frequency, capacitor C1 is shunted across R1. This attenuator now is called a compensated attenuator as shown in fig.a, and the same is redrawn as in fig.b

fig.a Compensated Attenuator

# **Pulse & Digital Circuits**

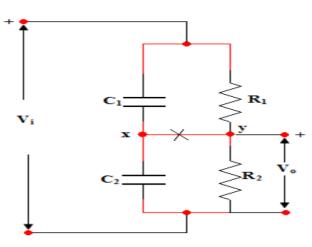

fig.b Compensated attenuator

R1,R2,C1,C2 form four arms of the bridge. The bridge is said to be balanced when R1C1=R2C2. Then no current flows in the branch xy. Hence for the purpose of computing the output, branch xy is omitted. The resultant circuit is

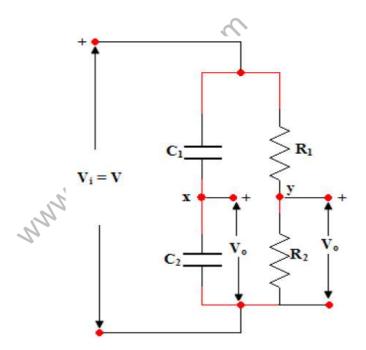

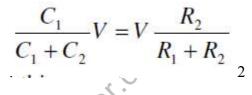

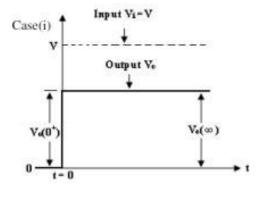

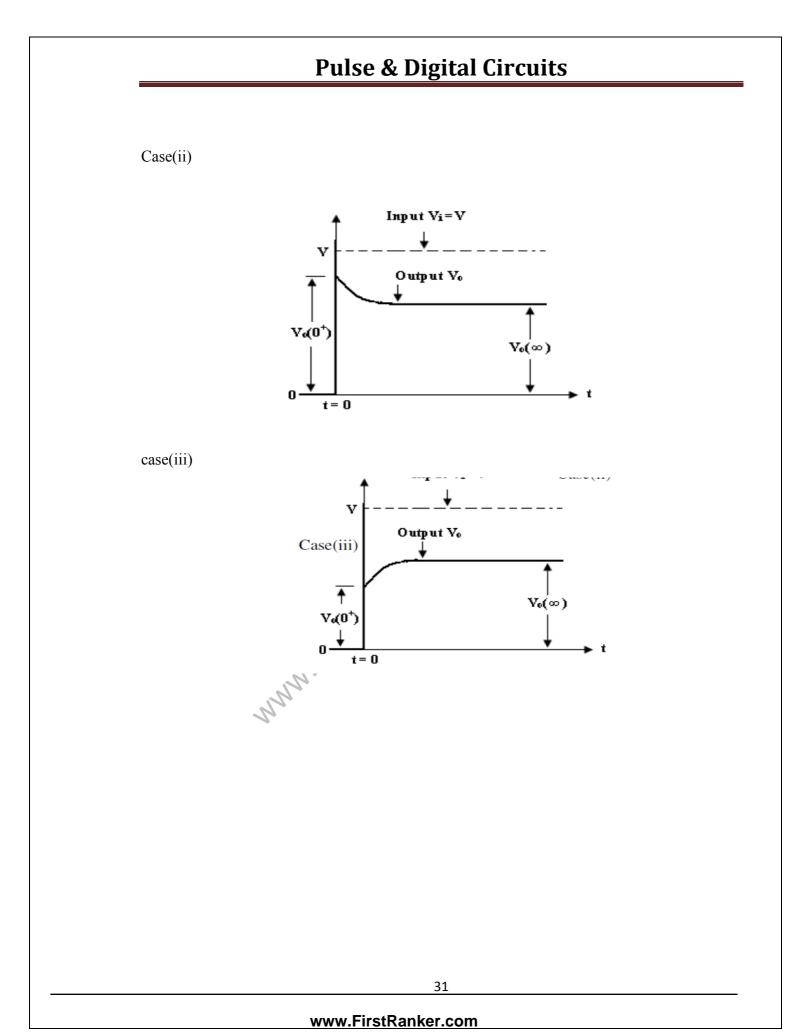

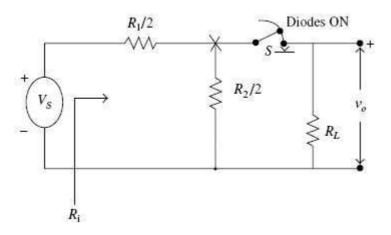

When a step voltage Vi=V is applied as input, the output is calculated as follows:

At t=0+, as the capacitors will not allow any sudden changes in voltage, as the Input changes the output also should change abruptly, depending on the values of C1 and C2.

## **Pulse & Digital Circuits**

$$V(0^+) = V \frac{C_1}{C_1 + C_2}$$

Thus, the initial output voltage is determined by C1 and C2.

As  $t \rightarrow \infty$ , the capacitors are fully charged and they behave as open circuits for dc. Hence the resultant output is

$$V_0(\infty) = V \frac{R_2}{R_1 + R_2}$$

Perfect compensation is obtained if,  $Vo(0+)=Vo(\infty)$

From this we get

C1R1=C2R2,or C1=(R2/R1)C2=Cp

and the output is  $\alpha Vi$

Hence following conditions(cases) arise.

(i) When C1=Cp, the attenuator is a perfectly compensated attenuator.

(ii) When C1>Cp , it is an over-compensated attenuator and

(iii) When C1<Cp, it is an under-compensated attenuator.

The responses of the attenuator for step input are shown in the following fig.

30

## **Pulse & Digital Circuits**

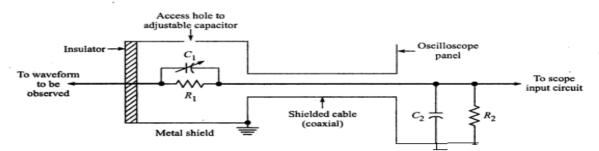

### 1.16 Application of attenuator as a CRO probe:

To measure the signal at a point in the circuit, the input terminals of the oscilloscope are connected to the signal point. Normally the point at which the signal is available will be at some distance from the oscilloscope terminals and if the signal appears at a high impedance level, a shielded cable is used to connect the signal to the oscilloscope. The shielding is necessary in this case to isolate the input lead from stray fields such as those of the everpresent power line. The capacitance seen looking into several feet of cable may be as high as 100 to 150 pF. This combination of high input capacitance together with the high output impedence of the signal source will make it impossible to make faithful observations of waveforms. A *probe* assembly, which permits the use of shielded cable and still keeps the capacitance low, is indicated in Figure 1.64.

### 1.17 RL and RLC Circuits and their response for step input.

#### **RL circuit**:

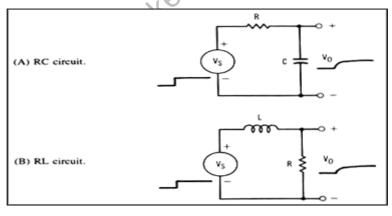

RL circuit is similar to RC circuit the circuit diagram represents RL circuit will be as follows it can be acts as high pass RL and low pass RL also.

## **Pulse & Digital Circuits**

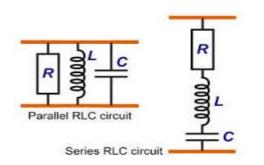

### **RLC circuits:**

There are two types of RLC circuits series RLC and parallel RLC will be as follows.

#### Step response of RL and RLC circuits:

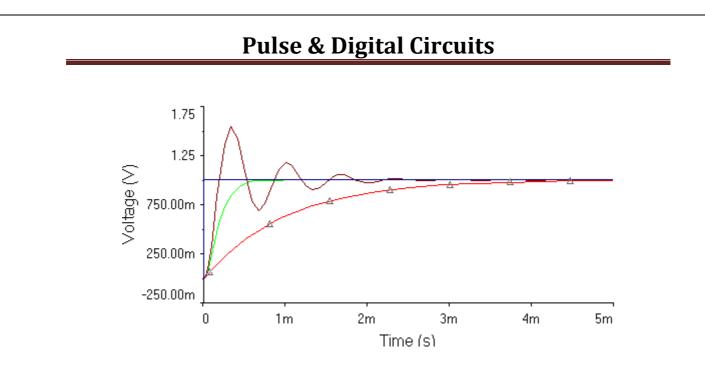

By solving above three cases we get the output as the waveforms which are under damped ,crictical damped and overdamped waveforms. The output waveforms will be as follows.

Fig. Response of RLC for step input.

### 1.18 Ringing circuit:

A circuit which provides un damped oscillations is called ringing circuit. If the damping is very small circuit rings for many cycles.for this circuit  $Q=\pi$  N.if Q=12,circuit will ring for 4 cycles

### **Important Questions:**

- 1. What is linear wave shaping?

- 2. What are linear elements give suitable examples?

- 3. What are linear wave shaping circuits?

- 4. What is high pass RC? explain how it acts as differentiator?

- 5. What is low pass RC? explain how it acts as integrator?

- 6. What is the time constant of RC circuit?

- 7. Draw the responses of high pass RC for STEP, PULSE, SQUARE inputs?

- 8. Draw the responses of low pass RC for STEP, PULSE, SQUARE inputs?

- 9. What is transmission error? how it can be defined?

- 10.What is attenuator? give its applications?

# **Pulse & Digital Circuits**

## 2. Non-Linear Wave Shaping

### Syllabus:

Diode clippers. Transistor Clippers. Clipping at two independent levels. Comparator – Applications of voltage Comparators – Diode Comparator. Clamping Operation. Clamping Circuits using Diode with Different Inputs. Clamping Circuit Theorem. Practical Clamping circuits. Effect of diodeCharacteristics on Clamping Voltage.

### 2.1 Diode clippers:

### **Basic Description**

As you know, diodes can be used as switches depending on the biasing type, reverse of forward. The clipping circuit also referred to as clipper, clips off some of the portions of the input signal and uses the clipped signal as the output signal.

Forward turning-on

Reversely turning-off

Ideal Diode – Switch Terminology

### 2.1. a Clipper Circuits

There are two types of clipper circuits, the series and parallel diode clipping circuits.

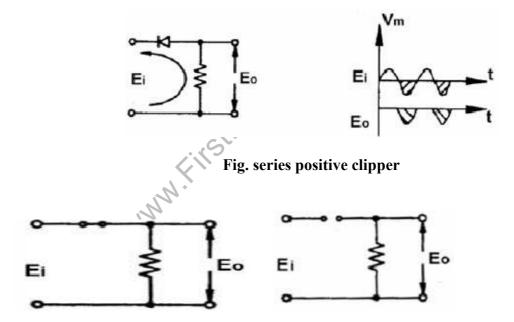

### 2.1 a.1 Series Diode Clipping Circuit

In these types of circuits, the diode is connected between the input and output voltage terminals

# **Pulse & Digital Circuits**

Fig: series negative clipper

As **Fig** reveals, the negative cycle of the input voltage can be clipped of by this type of series clippers. Reverse of the diode pins yields to a positive cycle clipping circuit as shown in **Fig**.

Diode operation as short and open circuits

## **Pulse & Digital Circuits**

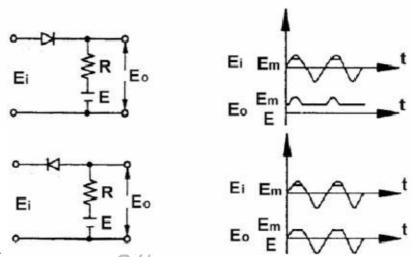

### **Diode clippers using bias**

Previous circuits clip the values larger or smaller than zero voltage. This voltage, technically called "threshold voltage" and can be changed to a desired value by inserting a D.C. voltage source. This is achieved in two different ways.

In the first type, the voltage source of Em (positive or negative) is connected through output terminals as in Fig Depending on the diode connection (normal12 or reverse), the values smaller or greater than Em is clipped and assigned as Em.

Note that if **Em** is negative, (where the voltage source is reversely connected) again the values smaller or larger than this negative value are clipped.

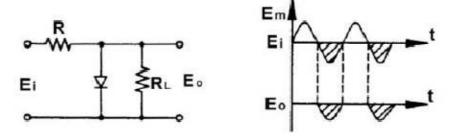

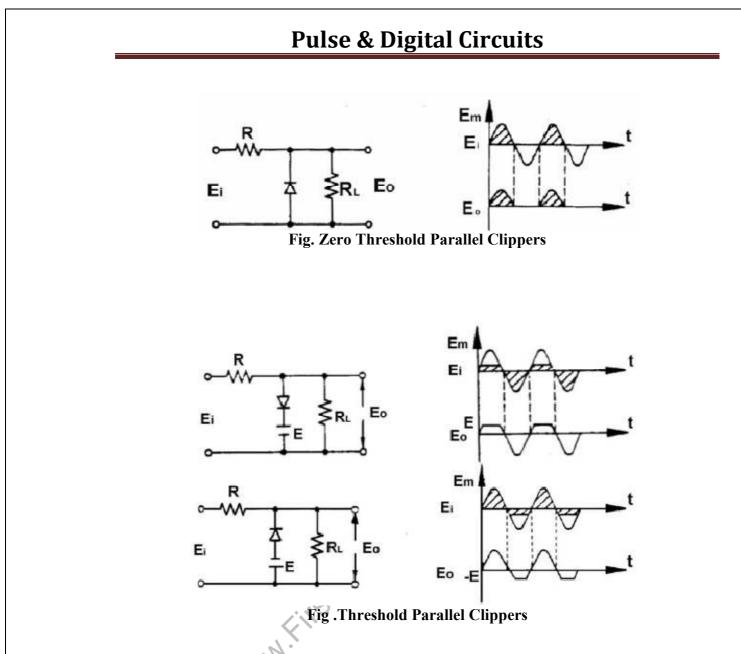

### **Parallel Diode Clipping Circuit**

In this type of clippers, the diode is connected between output terminals. The on/off state of diode directly affects the output voltage. These types of clippers may also have a non-zero threshold voltage by addition of a voltage series with diode.

Following figures illustrate the clipping process

37

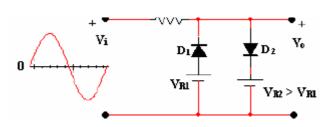

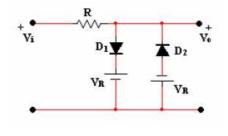

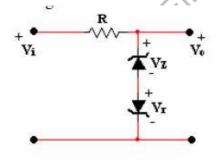

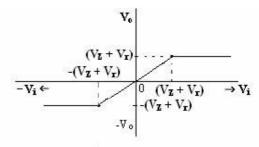

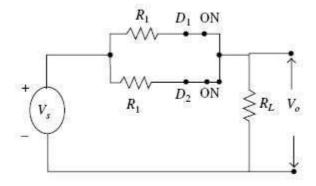

### 2.2 Double Diode Clipping

In single diode clipping circuit, the wave form is selected either above or below (but not on both sides) reference level. Two diode clippers may be used in parallel, series, or series-parallel to limit the output at two independent levels. Consider the circuit in Fig. side

# **Pulse & Digital Circuits**

The transfer curve has two break points, one at Vo = Vi = VR1 and

a second at Vo = Vi = VR2 has the following characteristics Vo

| Input voltage   | Output voltage | Diode states            |

|-----------------|----------------|-------------------------|

| Vi>VR2,         | Vo=VR1         | D1 is OFF and D2 is ON, |

| Vi < VR1,       | Vo =Vi         | D1 is ON D2 is OFF,     |

| VR1 < Vi < VR2, | Vo=VR2         | D1 and D2 are OFF.      |

Transfer characteristic of the slicer with input and output

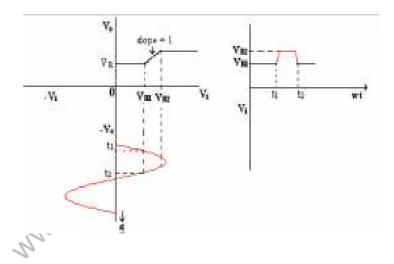

A combination of a positive peak clipper and a negative peak clipper, clipping the input symmetrically at the top and the bottom is called a limiter

39

# **Pulse & Digital Circuits**

The resultant transfer characteristic is as shown below.

### Fig.Transfer characteristic of a Limiter with input and output

Two avalanche diodes in series opposing, as indicated in fig below constitutes another form of double-ended clipper. If the diodes have identical characteristics then a symmetrical limiter is obtained. If the breakdown (zener) voltage is VZ and if the cut in voltage in the forward direction is Vy, then the transfer characteristic is as shown below. Transfer characteristic

Transfer characteristic

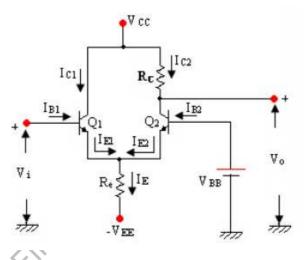

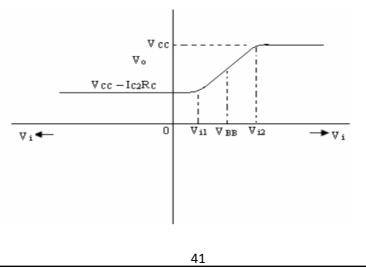

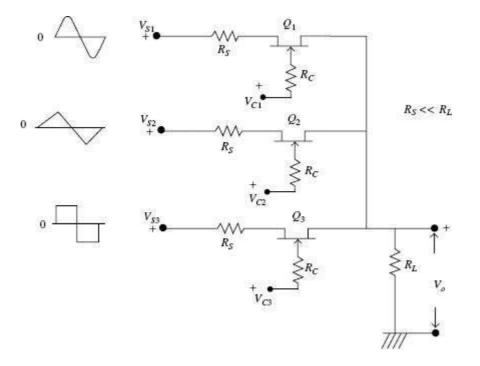

#### 2.3 Transistor clippers:

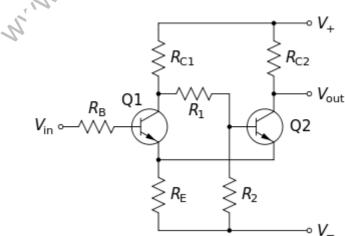

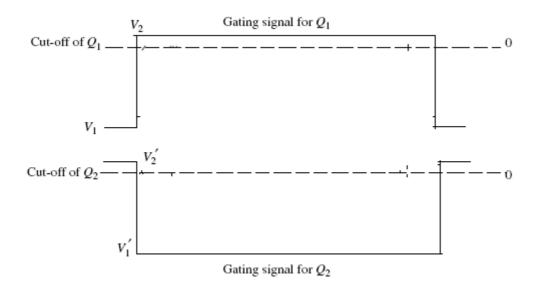

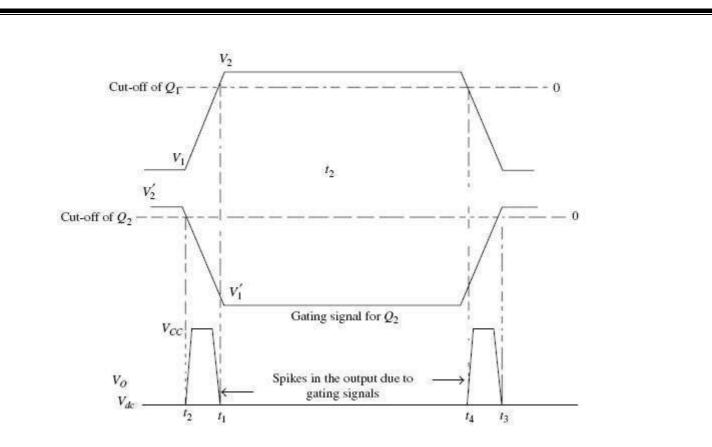

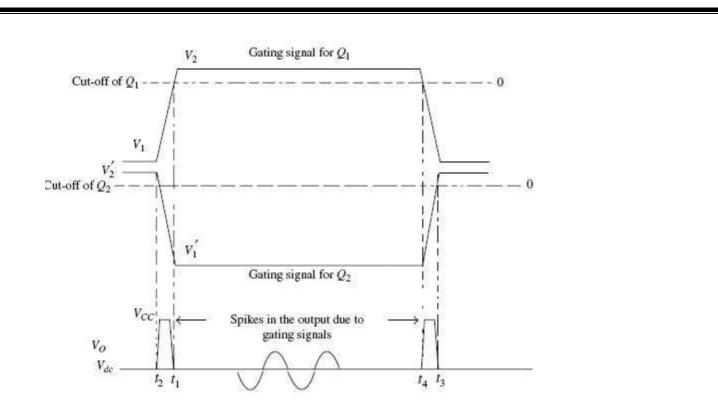

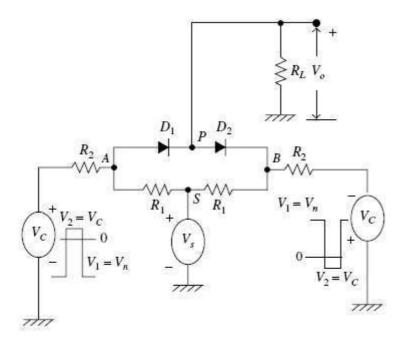

#### **Emitter-coupled transistor clipper:**

Consider initially that the input voltage Vi is negative enough to ensure that Q1 is in cutoff .Then only Q2 is carrying current. Consider that VBB has been adjusted so that Q2 is in its active region. As Vi increases Q1 will eventually come out off cutoff, both transistors will be carrying current and the input signal will appear at the output, amplified but not inverted. As Vi continues its excursion in the positive direction the common emitter will follow the base of Q1.The base of Q2 is fixed, a point will be reached when the rising emitter cuts off Q2 .Finally, the input signal is amplified but twice limited, once by the cutoff of Q1 and once by the onset of cutoff in Q2.

#### Fig.A two-level transistor clipper

The transfer characteristic is shown in fig below. Thus this circuit behaves as a two-level clipper. The region of linearity can be controlled by the choice of VBB.

www.FirstRanker.com

# **Pulse & Digital Circuits**

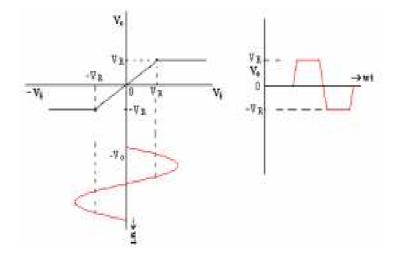

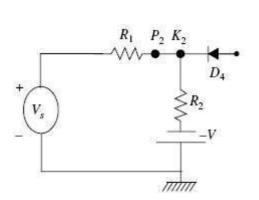

### **2.4 COMPARATORS:**

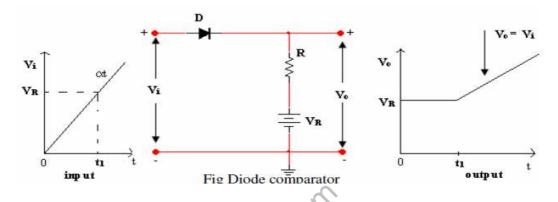

A comparator circuit is one which may be used to mark the instant when an Arbitrary waveform attains some reference level. Consider the simple clipping circuit for comparison operation.

For the sake of explanation let the input signal be a ramp as shown below.

This input crosses the voltage level  $vi = V_R$  at time t = t1.

The output remains quiescent at  $vo = V_R$  until t = t1 after which it rises with the input Signal

There is a sudden change in the slope of the output at the instant the input reaches  $V_{R}$ .

But due to ageing and due to temperature variations the diode, may not switch from OFF to ON at exactly t = t1. It may switch state at any instant after t1 and before t2.

www.FirstRanker.com

#### Input and output of the diode comparator

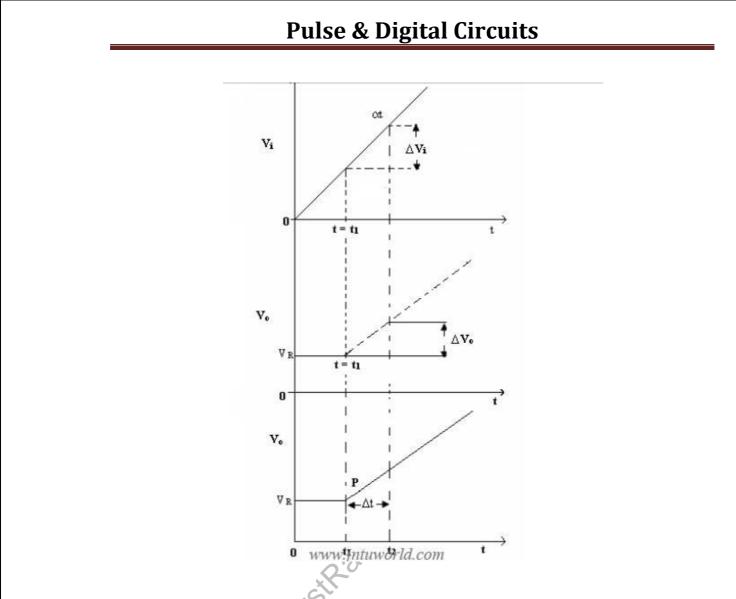

Hence, the break point (point at which device D changes state) may not exactly be at t1 but instead, there is a break region (t1 to t2).. Hence, there is a region of uncertainty which also, after the break point, the output follows the input i.e. has the same slope of the input. If this region of uncertainty is to be reduced, the response after the break point should be sharp. To achieve this amplifier may be placed before or after the comparator.

Consider the comparator circuit the response .To the left of the break point, the diode is OFF then the reverse incremental resistance of the diode, Rr is very much larger when compared to R. To the right of the break point the forward incremental resistance of the diode,  $R_f$  is very much smaller than R. If the break point is located at a point where r = R.

# **Pulse & Digital Circuits**

$$\Delta V_o = \Delta V_i \frac{R}{r+R} \approx V_i \quad \text{if } R \gg r$$

As  $\Delta V_o = \Delta V_i \frac{R}{r+R}$

f  $r = R$

$$\therefore \quad \frac{\Delta V_o}{\Delta V_i} = \frac{R}{R+R} = \frac{1}{2}$$

So the improvement is only half.

If a device is connected at the output of the comparator, this is required to be activated when the diode current is say, I and has a drop across R as IR.

If now an amplifier is connected at the output of the comparator so that this amplifier output activates the device.

Let the amplifier have a gain A. During  $\Delta t = t2 - t1$ , the output changes by

$\Delta Vo = V_2 - V_R$ , the delay in response is reduced to

Output of the comparator connected to an amplifier

$\Box$  –

Let the amplifier only amplify the change in the comparator input but not the reference voltage. The device to be activated is activated only when the drop across R is IR But now I = I/A, Hence the device is activated when the drop across R is RI/A since the diode current is amplified by A and the diode resistance i.e the dynamic resistance which varies inversely with current. Therefore it is evident that, the device to be activated by the

comparator will respond at a current such that

$$r = RA$$

$$\therefore \frac{\Delta V_o}{\Delta V_i} = A \frac{R}{r+R} = \frac{AR}{R+RA} = \frac{A}{1+A}$$

As  $A \to \infty$ ,  $\frac{\Delta V_o}{\Delta V_i} \to 1$

Without an amplifier  $\frac{\Delta V_o}{\Delta V_i}$  the transmission gain) was  $\frac{1}{2}$  and with an amplifier connected,

$\frac{\Delta V_o}{\Delta V_i}$  is 1. Which says that there is no marked improvement in the response of the comparator arrangement.

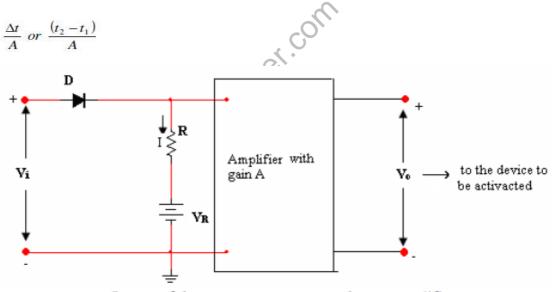

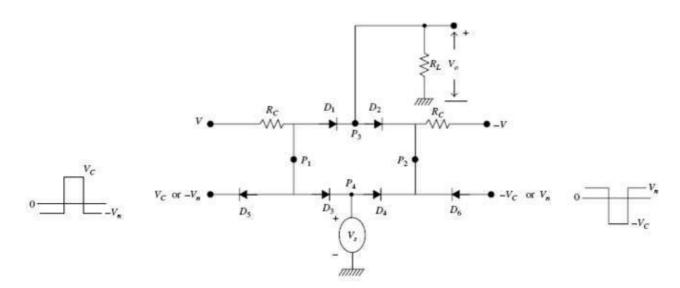

### 2.5 Some applications of comparators:

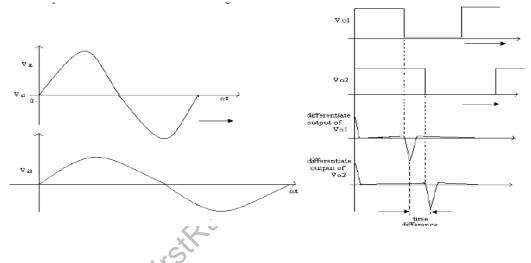

### (i) Measurement of time delays:

In the comparator shown before, if  $V_{R1}$  is the reference level in the first comparator (double differentiator) then a pulse is generated with a peak at t = t1. If  $V_{R2}$  is the reference level set in a second comparator then the pulse is generated with peak at t = t2.

Then the time difference between the two pulses is simply

$t2 - t1 = (V_{R2} - V_{R1})/\alpha$

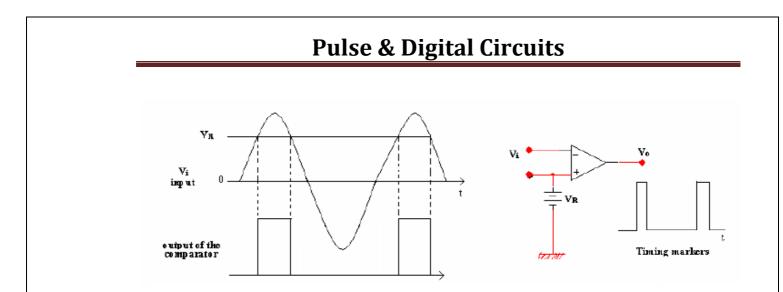

### (ii) Timing markers generated from sine wave:

If a sine wave is applied as input, when the input reaches VR output of the comparator is high till again the input reaches VR. Differentiate and clip negative spikes. We have positive spikes which can be implemented as timing markers.

(iii) **Phase meter:** Let two sinusoidal inputs having a phase difference be applied to a comparator whose reference voltage is zero.

Fig.The output pulses are differentiated and the time difference between the outputs spikes is proportional to the phase difference.

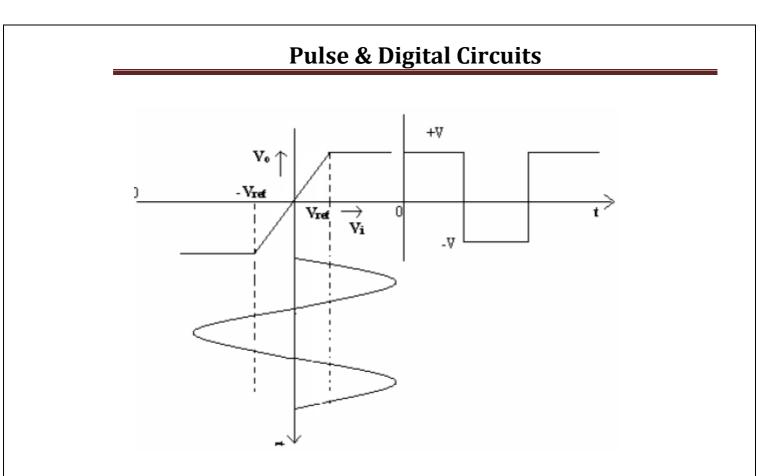

(iv) Square waves from sine waves: In regenerative comparator (Schmitt trigger) if the reference voltage is + Vref, the output goes to +V or -V

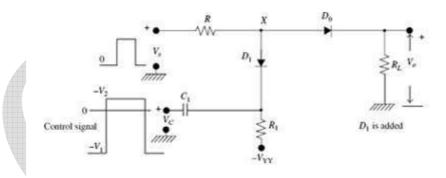

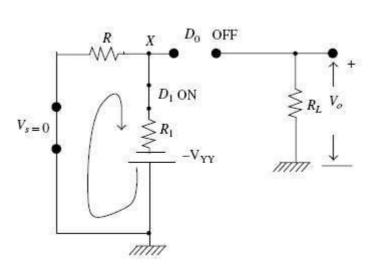

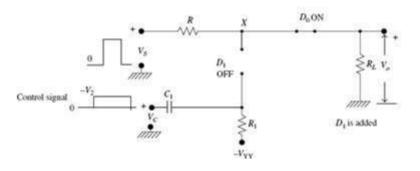

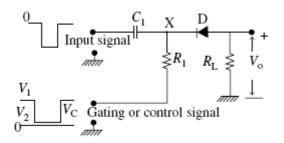

# **NON-LINEAR WAVESHAPING - CLAMPING CIRCUITS**

### 2.6 clamping operation:

### Introduction:

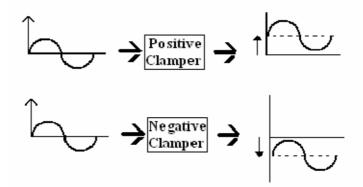

The establishment of extremity of positive or negative signal excursion at some reference level  $V_R$  is called Clamping. Clamping circuits introduce the dc component lost during transmission through a capacitive coupled network. Circuits that clamp the positive peak of the signal to zero level are called negative clampers and those that clamp the negative peak of the signal to zero level are called positive clampers. If a non-sinusoidal periodic signal is transmitted through a network having capacitive coupling, the dc component in the output is lost since the capacitor blocks the dc. If there arises the need once again that dc component is to be restored, this is done by a clamping circuit. A clamping circuit is, therefore, called a dc restorer or dc reinserted. As such, the output can be referenced to any arbitrarily chosen reference level.

# **Pulse & Digital Circuits**

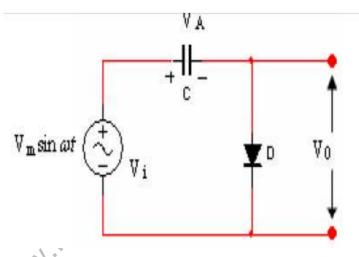

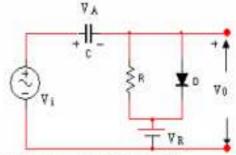

### The clamping circuit:

The circuit in fig below is the basic clamping circuit.

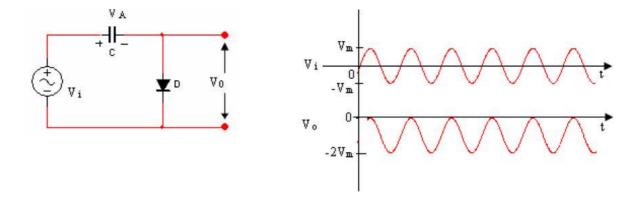

### Fig. Negative Clamping circuit

As the input rises from 0 to Vm in the first quarter cycle fig.4.2a, C charges to Vm. During this period, V0 = 0. i.e. the output is zero for the first quarter cycle since D conducts. The input falls after the first quarter cycle. Vi<Vm, the charge on the capacitor. As a result the diode is reverse biased by a voltage (Vi -Vm). Hence D is OFF.

V0=Vi - Vm ----- 1

The voltage across C remains unchanged.

From equation .1----.If Vi = 0, V0 = -Vm

And if, Vi = -Vm, V0 = -Vm - Vm = -2Vm

During the next cycle, the positive peak of the output just reaches the zero level. Hence in the output, the positive peak is clamped to zero level and this is repeated for succeeding cycles. The input, output waveforms are represented in fig.2

Fig.2 input – output waveforms of negative clamp

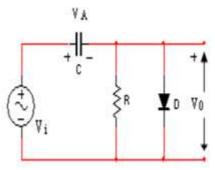

The input to this circuit is a sinusoidal with zero reference level. The output is referenced to - Vm and the positive peak is clamped to zero. When the input decreases, to clamp the positive peak to zero level, the voltage across the capacitor should change to the peak amplitude of the new input. But there is no discharge path for the capacitor to discharge. For this a resistance R is provided in shunt with the diode D fig.3

Fig. clamping circuit with R shunted across diode D

www.FirstRanker.com

Fig. a) input b) Output when  $R = \infty c$ ) output with finite R

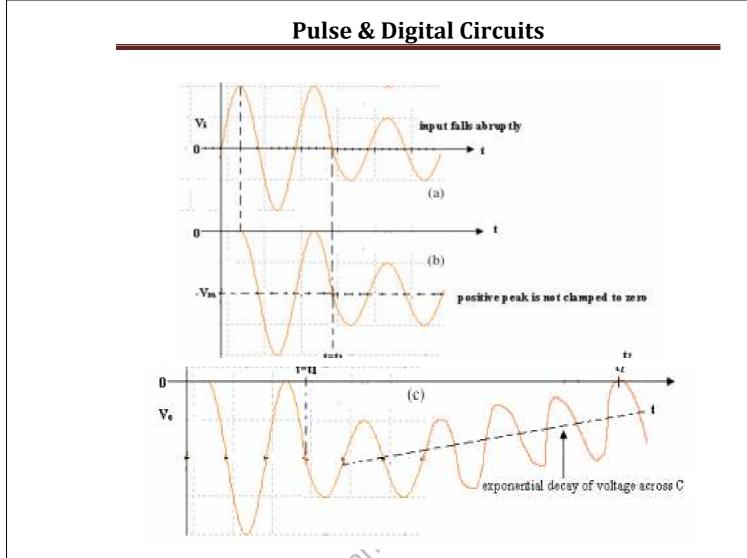

At t = t1, if the input amplitude is abruptly reduced, as the voltage across the capacitor cannot change instantaneously, the positive peaks will not reach zero level. But now as the charge on C is going to discharge, as the voltage across the capacitor varies exponentially with a time constant  $\tau$ =RC, the output reaches zero level at t = t2, the positive peak is again clamped to zero, after few cycles

#### Fig. Output with expanded time scale in the neighborhood of a positive peak

In the vicinity of a positive peak D conducts and at t = t, V0=0. If there were to be no diode, the output should have followed the dashed line with the peak at t = t2. But because of the diode, the output in zero from  $t_2$  to t2 and in the subsequent cycles the positive peaks of the sinusoidal are clamped to zero.

### **2.7 Clamping circuit theorem:**

Under steady state conditions the area under the forward biased condition and the area under the reverse biased condition are related as  $A_f/A_r=R_f/R$

#### proof:

for forward biased condition charging of capacitor can be done and charge stored on capacitor is  $Q1=A_{f/}R_{f}$ .

for reverse biased condition discharging of capacitor can be done and CHARGE LOST BY capacitor is  $Q2=A_r/R$ .

under steady state conditions charge gained by the capacitor equal to charge lost hence we can get

$$A_f/A_r = R_f/R$$

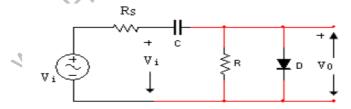

### 2.8 Clamping circuit with diode and source resistances:

Consider now the internal resistance of the source, R<sub>S</sub>.as shown in Fig.

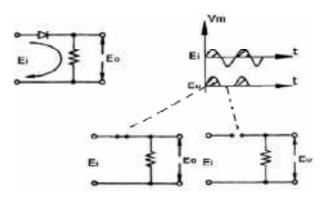

When the input is applied, the output reaches the steady-state value after a few cycles and the positive peaks are clamped to zero. Consider the equivalent circuits

(i) When the diode is ON,

# **Pulse & Digital Circuits**

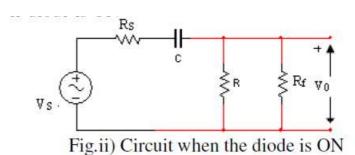

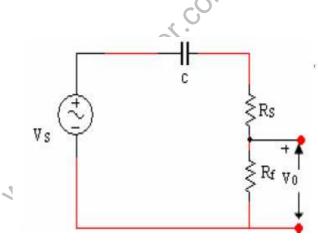

(i) When the diode is ON

As R<sub>f</sub> << R, this circuit reduces to

Fig.ii) Circuit when the diode is ON

This circuit, for the purpose of computing the output may be redrawn as fig.iv

### Fig.Circuit to calculate the output when the diode is ON

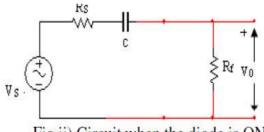

(ii) when the diode is OFF

# **Pulse & Digital Circuits**

circuit when D is OFF

As Rr >> R, this circuit reduces to

Again, for computing the output this circuit is redrawn as in Fig

Fig.Circuit to calculate the output when the diode is OFF

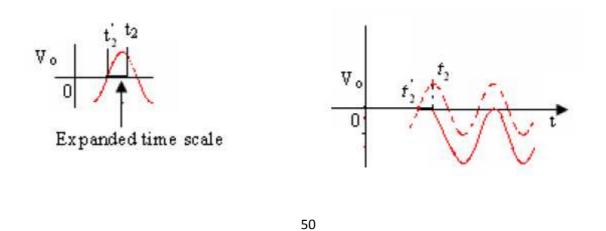

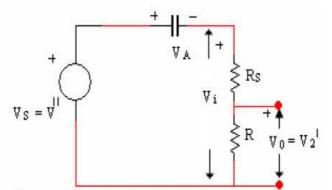

### 2.9 Practical clamping circuits

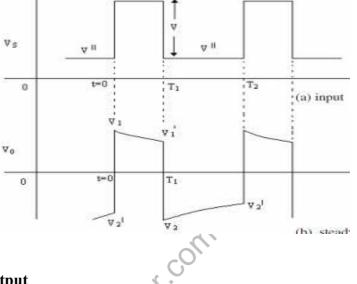

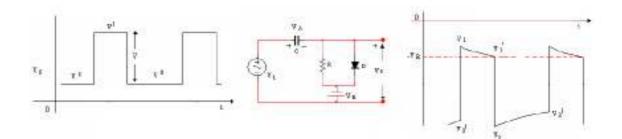

If a square wave is applied as input to a clamping circuit, the output reaches the steady state value after a few cycles.

Hence for the input in Fig.(a) the output of the clamping circuit is given in (b).

(a) input

(b) steady-state output

### Input and steady-state output of the clamping circuit

The output at steady-state is as in figure above with voltage levels  $V^1$ ,  $V^{11}$ ,  $V_2$  and

### **Pulse & Digital Circuits**

Input and steady-state output of the clamping circuit

The output at steady-state is as in figure above with voltage levels  $V_1$ ,  $V_1^1$ ,  $V_2$  and  $V_2^1$ . This output can be plotted to scale if the voltages  $V_1$ ,  $V_1^1$ ,  $V_2$  and  $V_2^1$  are calculated. To calculate these four unknowns, we need four equations and these four equations are obtained as follows.fig.

(a) consider the situation at t = 0-

At t = 0-,  $Vs = V^{11}$  and  $V_0 = V_2^{11}$

The diode is reverse biased and the corresponding equivalent circuit is

2

....

The voltage across the capacitor terminals at t=0- is

$V_A(0-) = V_s - V_i \qquad \dots$

$$V_s = V^{11}$$

and  $V_2^1 = V_i \frac{R}{R_s + R}$

$\therefore V_i = V_2^1 \frac{(R_s + R)}{R}$

Substituting the values of Vs and Vi in equation 2

:.

$$V_A(0-) = V^{11} - V_2^{-1} \frac{(R_s + R)}{R}$$

------ 3

(b) Consider the situation at the instant t = 0+

At t=0+,  $V_s = V^1$  and  $V_0 = V_1$ . the diode is ON and the corresponding equivalent circuit is

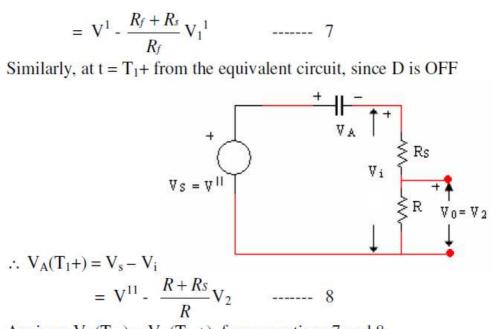

# **Pulse & Digital Circuits** Vs = VThe voltage across the capacitor terminals at t = 0 + is $V_{A}(0+) = V_{s} - V_{i}$ $= V^{1} - V_{i}$ $\mathbf{V}_1 = \mathbf{V}_i \; \frac{R_f}{R_s + R_f} \; ,$ $\therefore V_i = \frac{(R_s + R_f)}{R_f} V_1$ $\therefore \mathbf{V}_{\mathbf{A}}(0+) = \mathbf{V}^1 - \frac{(R_s + R_f)}{R_f} \mathbf{V}_1$ 4 Since the voltage across the capacitor cannot change instantaneously $V_A(0-) = V_A(0+)$ Hence, from equations 3 and 4 $V^{11} - \frac{R+Rs}{R}V_2^{-1} = V^1 - V_1 \frac{Rs+R_f}{R_f}$ 5 The peak-to-peak amplitude of the input is V. Therefore $V = V^1 - V^{11}$ From equation 5, $V = V^1 - V^{11} = V_1 \frac{R_s + R_f}{R_f} - \frac{R + R_s}{R} V_2^1$ ------6 Once again consider the situation at $t = T_1^-$ , $V_s = V^1$ and $V_0 = V_1^{-1}$ and the diode is ON 1 ۷A $V_A(T_{1-}) = V_s - V_i$ $V_S = V$ 56

# **Pulse & Digital Circuits**

Again as  $V_A(T_1-) = V_A(T_1 +)$ , from equations 7 and 8

Further at t = 0+,  $V_0 = V_1$  and in the interval 0 to  $T_1$ ,  $V_0$  decays with a time constant  $(R_f+R_s)C$

Hence,

$$V_1^{\ 1} = V_1 e^{\frac{-T_1}{(R_f + R_s)C}}$$

10

Similarly in the interval  $T_1$  to  $T_2$ , the diode is reverse biased and the circuit time constant

is  $(R_s+R)C$

The voltage  $V_2$  decays to  $V_2^{\ 1}$

$-(T_2-T_1)$

$$V_2^{\ 1} = V_2 e^{\frac{-(I_2 - I_1)}{(R_s + R)C}}$$

------ 11

12

# **Pulse & Digital Circuits**

Equations 6, 9, 10 and 11 will enable us to determine the voltage  $V_1$ ,  $V_1^1$ ,  $V_2$  and  $V_2^1$ . If in the above circuit  $R_s = 0$ .

Equations 6 and 9 reduce to

$V = V_1 - V_2^{\ 1} = V_1^{\ 1} - V_2 \qquad ------$

It is evident from the above discussion that the output is independent of the levels  $V^1$  and  $V^{11}$  associated with the input and is only determined by the amplitude V.

Subtracting equation 9 from equation 6

$$\frac{R_f + R_s}{R_f} (V_1 - V_1^{-1}) - \frac{R + R_s}{R} (V_2^{-1} - V_2) = 0$$

------ 13

If  $V_1 - V_1^{-1} = \Delta_f$  and  $V_2^{-1} - V_2 = \Delta_r$ From Equation 13

$$\frac{R_f + R_s}{R_f} \Delta_{\rm f} = \frac{R + R_s}{R} \Delta_{\rm r}$$

$$\Delta_{f} = \frac{R_{f}}{R_{s} + R_{f}} \cdot \frac{R + R_{s}}{R} \Delta_{r}$$

If Rs << R

$$\Delta_{f} = \frac{R_{f}}{R_{s} + R_{f}} \Delta_{r} ,$$

where  $\Delta_f$  is the tilt in the forward direction and  $\Delta_r$  is the tilt in the reverse direction Let Rs << R<sub>f</sub>

Then  $\Delta_{f} \approx \Delta_{r}$

# **Pulse & Digital Circuits**

### A clamping circuit that clamps the output to a reference voltage V<sub>R</sub>:

The following clamping circuit similar to that we have studied earlier, except for the fact that a reference voltage  $V_R$  is included.

Fig.1 Circuit that clamps the positive peak of the input to VR

To obtain the steady-state response of the circuit, first assume that  $V_R$  is zero. Then this circuit is clamping circuit that clamps the positive peak of the input signal to  $V_\gamma$ . Now the steady-state response for the input of an unsymmetrical square wave, will be as follows.

Solving four equations (we have discussed earlier) the values of  $V_1$ ,  $V_1^1$ ,  $V_2$  and  $V_2^1$  can be evaluated. To each of these values calculated add  $V_{R}$ . With the result, the positive peak in the output is clamped to  $V_R$ .

The positive peak of the input clamped to -VR

#### www.FirstRanker.com

27

# **Pulse & Digital Circuits**

### 2.10 Effect of diode charecterestics on clamping voltage:

The diode characteristics will also effect the voltage as diode voltage is the clamping voltage,

$$I_{\rm cl} = I_o e^{V_{\rm cl}/\eta V_T}$$

will be the diode current. For charging of capacitor resistor voltage is

equal to

$$R = V_{\rm A} - V'' = V - V_{\rm cl}$$

$$V_{\rm cl} << V. \text{ Hence } V - V_{\rm cl} = V$$

Charging current=discharging current

$$I_{cl} = \frac{V}{R} = I_o e^{(V_{cl}/\eta V_T)}$$

$$\frac{V}{I_o R} = e^{(V_{cl}/\eta V_T)}$$

$$V_{cl} = \eta V_T \ln \frac{V}{RI_o}$$

$$dV_{\rm cl} = \eta V_T \frac{dV}{V}$$

From the above equation we can say that the diode will effect the voltage as diode voltage is the clamping voltage,

### Important Questions:

1.what is clipping?what are the types of clippers?

2.what is non linear wave shaping?

3.what is clamping ?what are the types of clamping?

4.explain the effect of diode charecterestics on clamping voltage?

5.state clamping circuit theorem?

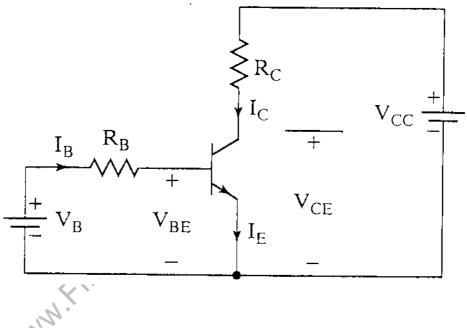

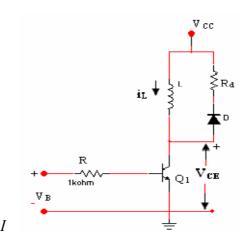

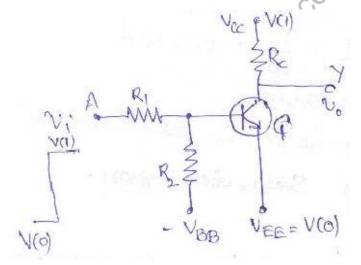

### 3. <u>SWITCHING CHARECTERESTICS OF DEVICES</u> <u>SYLLABUS:</u>

Transistor and diode as a Switch - Switching times of a transistor. Transistor acts as a switch, Breakdown voltage consideration of transistor, saturation parameters of transistor and their variation with temperature, design of transistor switch, transistor switching times.

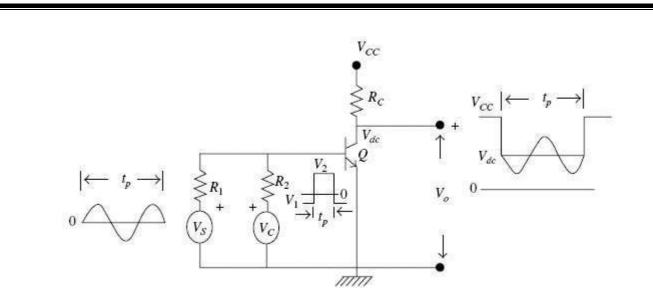

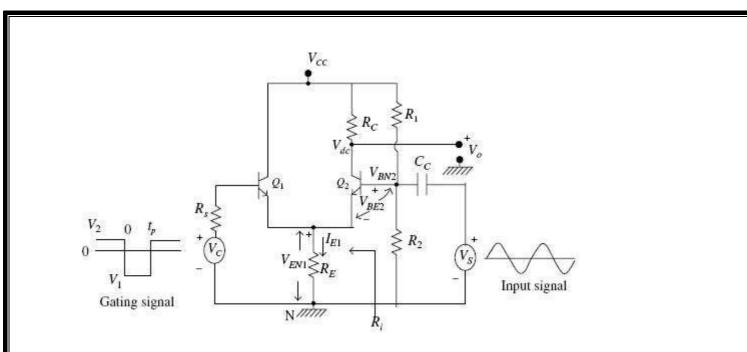

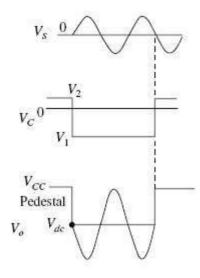

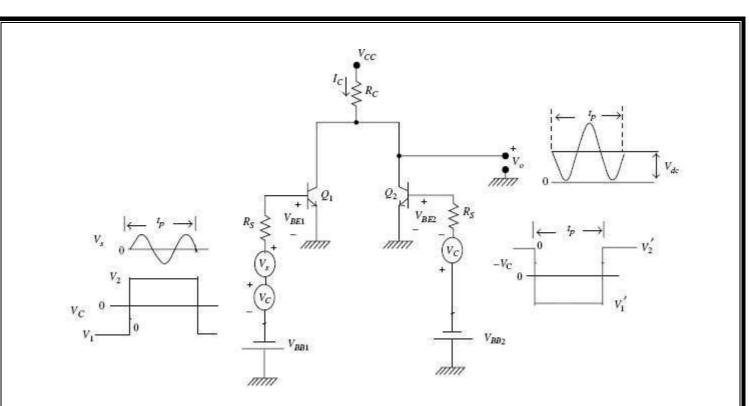

### Fig. Transistor as a switch

Above diagram represents the operation of transistor as a switch.

The transistor operates as a switch in two regions mainly

- 1. Saturation region: In this region transistor acts as closed switch.

- 2. Cut-off region: In this region transistor acts as closed switch

By applying KCL to above circuit,

## **Pulse & Digital Circuits**

$$\begin{split} I_B = \frac{V_B - V_{BE}}{R_B} \\ V_{CE} = V_{CC} - I_C R_C \\ V_{CE} = V_{CB} + V_{BE} \\ V_{CB} = V_{CE} - V_{BE} \end{split}$$

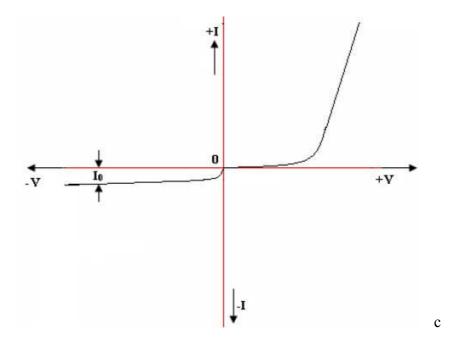

### 3.2 Switching characteristics of devices

### Diode as a switch:

A PN junction diode can be used as a switch. When diode is forward biased, the switch is said to be in the ON state and in reverse-bias, the switch is in the OFF state. The V-I Characteristic of a PN junction diode is shown here.

#### V-I characteristic of a PN diode

The diode current is given by the relation

$$I = I_0 \left( e^{\frac{V}{\eta V_T}} - 1 \right)$$

Where V is the bias voltage,  $\eta = 1$  or 2 depending on whether the diode is Ge or Si and VT is the Volt-equivalent for temperature and at room temperature VT = 26mV.

### **Pulse & Digital Circuits**

$$e^{\frac{V}{\eta V_T}} >> 1,$$

If

equation 5.1 reduces to

$$I = I_0 e^{\frac{V}{\eta V_1}}$$

When the diode is forward biased V is positive and I is a positive current which varies exponentially with the variation of V. When the diode is reverse-biased V is a negative voltage and the current I now flows in the opposite direction. I = -I0, the reverse saturation current gets doubled for every 100C rise in temperature.

When a diode is used as a switch, the device should be ON or OFF depending on the polarity of the signal applied to change state.

### Junction diode switching times:

#### Reverse recovery time of the diode:

Let the diode be ON for some time, as a result there is a large current due to injected hole or electron density.

63

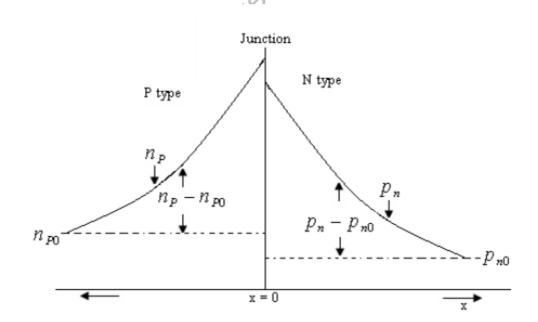

Fig.a Minority carrier density distribution as a function of x, the distance from the junction when the diode is ON

$p_{n0}$  = density of holes on the n-side at equilibrium  $n_{p0}$  = density of electrons on the P-side at equilibrium  $n_p$  = density of electrons on the P-side when forward biased  $p_n$  = density of holes on the n-side when forward biased  $p_n - p_{n0}$  = injected or excess hole density on the n-side  $n_p - n_{p0}$  = injected or excess electron density on the P-side

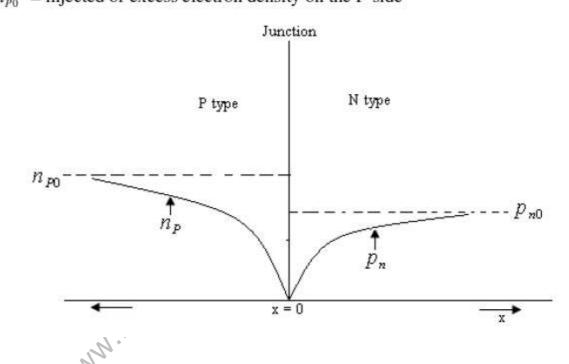

When the diode is ON the number of minority carriers is large fig (a). When the polarity of the external voltage is suddenly reversed, the diode forward current when ON being large is to be reduced to reverse current which is very small. But this is not happened as it takes a finite time delay for the minority carrier density distribution to take the form shown in fig. During this period the injected minority carrier density will drop to zero and the minority carrier density reaches the equilibrium value.

www.FirstRanker.com

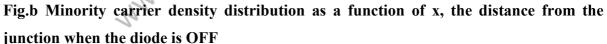

As long as the voltage Vi = VF till t1, the diode is ON. The forward resistance of the diode being negligible when compared to RL, therefore

$$I_F = \frac{V_F}{R_L}$$

At t = t1, the polarity of Vi is abruptly reversed, i.e.Vi = -VR and  $-I_R = \frac{K}{R_L}$  until t = t2 at which time minority carrier density pn at x = 0 has reached the equilibrium value pn0. At t = t2 the charge carriers have been swept, the polarity of the diode voltage reverses, the diode current starts to decrease. The time duration, t1 to t2, during which period the stored minority charge becomes zero is called the **storage time ts**.

The time interval from t2 to the instant that the diode has recovered (V = -VR) is called the **transition time,t**<sub>T</sub>.

The sum total of the storage time,ts and the transition time,tt is called the reverse recovery time of the diode, trr.

$\therefore t_{rr} = t_s + t_t$

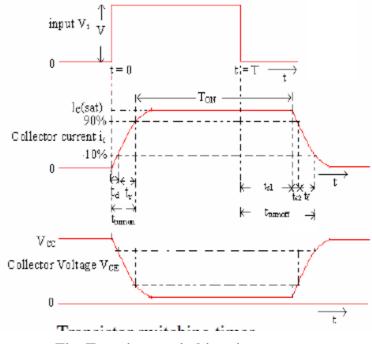

### Transistor switching times

Let the input to the transistor switch be a pulse of duration T.

When a pulse is applied, because of stray capacitances, collector current will not reach the steady state value instantaneously. To know exactly when the device switches into the ON state and also into the OFF state we define the following switching times of the transistor.

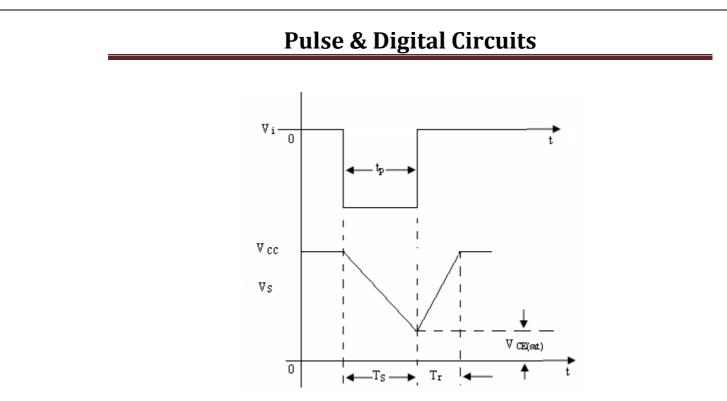

Fig. Transistor switching times

**Delay Time, td:** It is the time taken for the collector current to reach from its initial value to 10% of its final value, If the rise of the collector current is linear, the time required to rise to 10%IC(sat) is 1/8 the time required for the current to rise from 10% to 90% IC(sat). It is given as

### **Pulse & Digital Circuits**

$$\mathbf{t}_{\mathrm{d}} = \frac{1}{8}t_{r}$$

Anny.

where tr is the rise time

**Rise Time,tr** : It is the time taken for the collector current to reach from 10% of its final value to 90% of its final value.

However, because of the stored charges, the current remains unaltered for sometime interval ts1 and then begin to fall. The time taken for this current to fall from its initial value at ts1 to 90% of its initial value is ts2. The sum of these ts1 and ts2 is approximately ts1 and is called the storage time.

**Storage time, ts:** It is the time taken for the collector current to fall from its initial value to 90% of its initial value. Storage time

$$t_s \cong \tau_s \ln \frac{I_{B1} - I_{B2}}{I_{B\min} - I_{B2}}$$

$I_{B1}$  is the base current when the pulse amplitude is V(=12 V) and  $I_{B2}$  is the base current when the pulse amplitude is zero.

Fall time,  $t_f$ : It is the time taken for the collector current to fall from 90% of its initial value to 10% of its initial value.

### UNIT III & IV

### Multivibrators

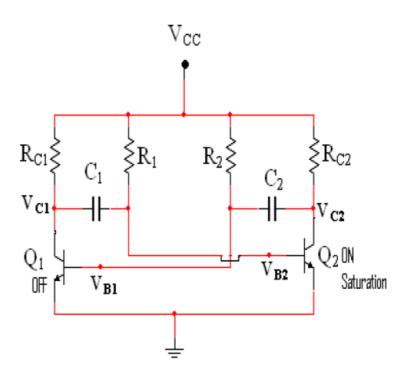

Multi vibrators are cross-coupled two-stage regenerative amplifiers acting as switching circuits. Multi vibrators are broadly classified as

- 1. Bistable multi or binary or Flip-Flop

- 2. Monostable multi or One shot multi or univibrator

- 3. Astble multi or Freerunning multi

Multivibrators are extensively used in digital and switching applications. A bistable multivibrator remains in one of the stable states until we are asked to change. Hence this circuit is essentially used as a memory element in digital circuits..

A monostable multi has only one stable state and one quasi-stable state. Initially the multiis in stable state. After the application of a trigger, the multi goes into the quasistablestate and stays there for a finite time and will return back to the initial stable state. Such acircuit is used as a gate. Other type of multivibrator is an Astable multi which has two quasistable states. Thismeans that change of state occurs in the multi simultaneously. So, the output of this multiis a squarewave. The output of an astable multi is normally used as a clock signal indigital circuits.

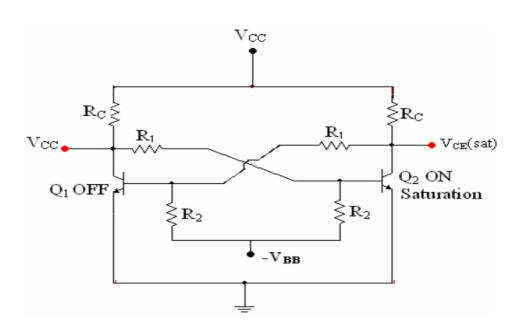

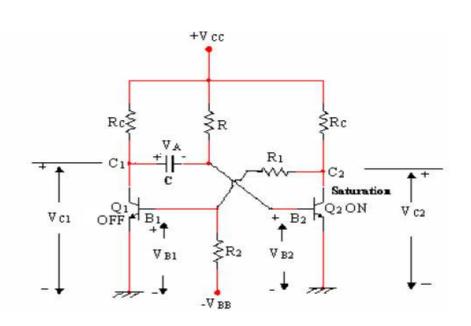

### **Bistable multivibrators**

#### Introduction:

This circuit has two devices Q1 and Q2. Let initially be Q1, OFF and Q2 ON. On the application of a trigger Q1 goes to ON and Q2 goes to OFF. When next trigger is applied Q1 goes OFF and Q2 goes ON. If the ON device is driven in to saturation, the Binary is called saturating Binary. If on the other hand, the ON device is held in the active region, the binary is called a

non-saturating binary.

Consider two types of Bistable multivibrator circuits.

1. Fixed bias binary

2. Self bias binary

#### **Fixed bias binary:**

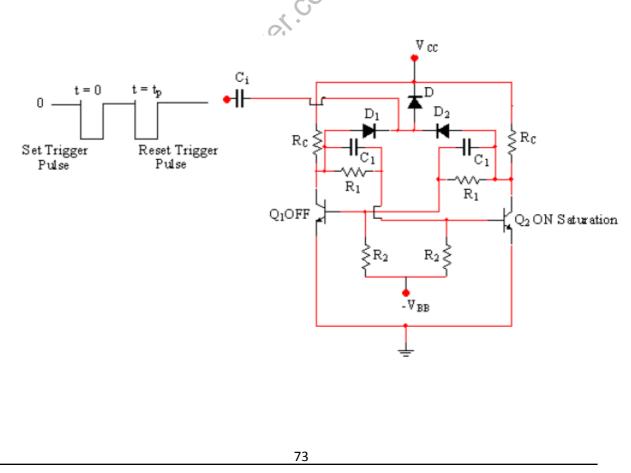

The circuit shown in fig.below is a fixed-bias binary

Let initially Q1 be OFF and Q2 be in ON. Then the voltage at the first collector is  $V_{CC}$  and the voltage at the second collector is  $V_{CE}(sat)$ . If a negative trigger is applied at the base of the ON device (Q2), Q2 goes into the OFF i.e. its collector voltage rises to  $V_{CC}$ . Consequently Q1 goes into the ON state and its collector voltage falls to VCE(sat).

on

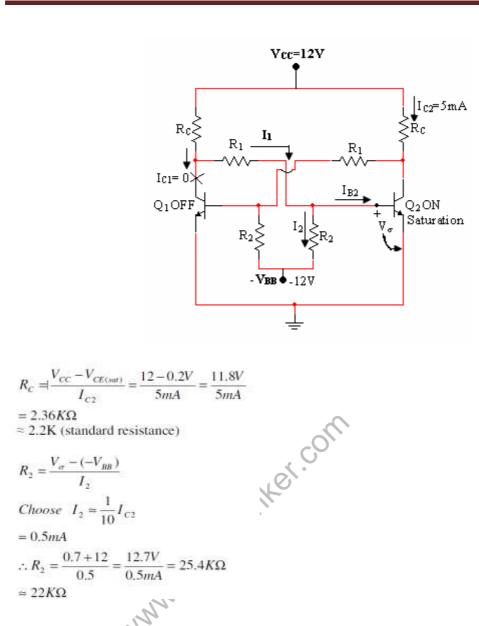

### Design of a fixed bias binary:

Design a fixed bias binary with supply voltages +12V, NPN silicon devices having VCE(sat)= 0.2V, VBE(sat)= 0.7V and  $h_{FEmin}$ =50 are used. Assume  $I_C = 5mA$ .

# **Pulse & Digital Circuits**

If Q2 is in saturation

# **Pulse & Digital Circuits**

$$\begin{split} I_{B2} &= 1.5I_{B2\min} \\ &= 0.15 \, mA \\ I_1 &= I_2 + I_{B2} \\ &= 0.5 \, mA + 0.15 \, mA = 0.65 \, mA \\ R_c &+ R_1 = \frac{V_{cc} - V_{\sigma}}{I_1} = \frac{12 - 0.7}{0.65 \, mA} = \frac{11.3V}{0.65 \, mA} = 17.38 \, K\Omega \\ R_1 &= (R_c + R_1) - R_c \\ &= 17.38 - 2.36 = 15.02 \, K\Omega \end{split}$$

The circuit, so designed, with component values indicated is shown below:

**3.4 Resolution time of a binary**:

It is the sum of settling time and transition time of a binary is called resolution time.

### 3.5 Methods of improving resolution time:

- 1. By reducing stray capacitances.

- 2. By not allowing transistors to go into saturation.

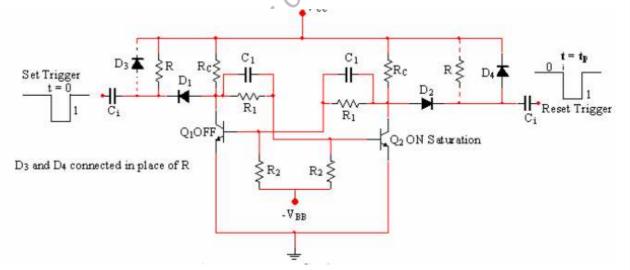

### 3.6 Methods of triggering a binary:

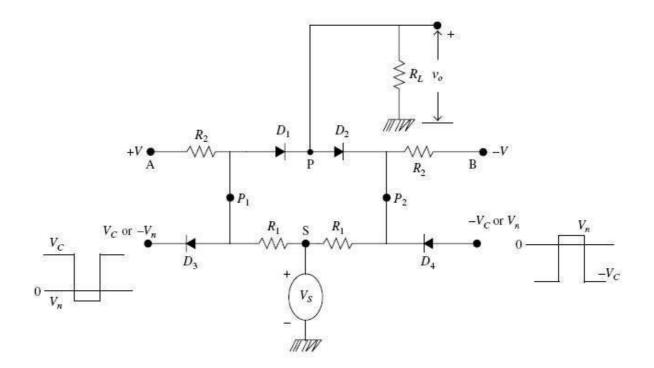

To change the binary from one stable state to the other, a pulse of short duration with sufficient amplitude (called trigger) of proper polarity should be applied at the input(output) of an active device the circuit. The trigger can be a dc trigger or it can be a pulse trigger. There are two triggering methods to change the state of multivibrator.

- 1. Unsymmetrical triggering

- 2. Symmetrical triggering.

### **Unsymmetrical triggering:**

In unsymmetrical triggering, one trigger pulse, taken from a source, is applied at one point in the circuit. The next trigger pulse taken from a different source is applied at a different point in the circuit as shown below.

### Unsymmetrical triggering of a binary

Let the trigger be applied to the collector C1 of the circuit at t=0. If Q1 is OFF, D1 is ON and this negative pulse appears at the base of Q2 as the first collector and second base are connected. Q2 goes into the OFF state and Q1 into the ON state. The next through C1 trigger pulse, i.e. the Reset pulse, is applied through D2 at the second collector C2 which is coupled

to the first base through C1. Q1 now goes into the OFF state and Q2 into the ON state. Unsymmetrical triggering is used to generate a gated output, the width of this gate must be at least equal to the spacing between two successive triggers. To prevent the loading down problem from the trigger source, R should be large. But when a trigger is applied, a charge is built up on the condenser Ci. If the charge is to be quickly removed before the application of the next trigger signal at this terminal, R should be small. So while choosing the value of resistance R a compromise is necessary single resistance cannot simultaneously satisfy these two requirements. Hence in place of R, diodes D3 and D4 are used. When a pulse appears, the diode is OFF (D3 or D4), a large reverse resistance of the diode appears in place of R. Otherwise the diode is ON offering negligible resistance so that the charge on the capacitance can be quickly removed.

### Symmetrical triggering:

In symmetrical triggering, one triggering pulse generator is taken to change from one stable state to the other in one direction. The same is used to change the state in reverse direction also. This method of triggering is normally used in counters.

## **Pulse & Digital Circuits**

#### Fig. Symmetric triggering of binary

The purpose of D is similar to the diodes D3 and D4 used earlier. The first trigger pulse makes D1 conduct and this pulse is coupled to the base of Q2 and drives Q2 into the OFF state and Q1 into the ON state. The next trigger pulse applied at  $t = t_p$  is coupled to the base of Q1 as D2 is now ON. Hence Q1 again goes into the OFF state and Q2 into the ON state. D1 and D2 are called steering diodes as these diodes steer the trigger pulse train.

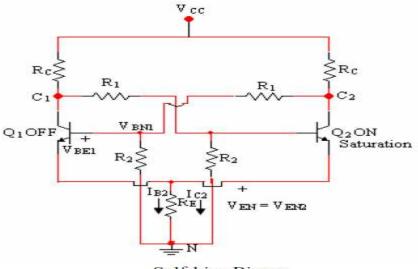

### Self-bias binary :

In a fixed bias binary there are two separate sources, VCC and VBB. Instead two we can design a binary with one power supply using self-bias method.

Self-bias Binary

Let  $Q_2$  be ON and in saturation, in the initial stable state. As a result  $I_{B2}$  and  $I_{C2}$  flow through  $R_E$  developing a voltage  $V_{EN}$ . The voltage between the base emitter terminals of Q1 is  $V_{BE1}$  and it is  $V_{BE1} = V_{BN1} - V_{EN}$

If this voltage reverse biases the emitter diode of Q1, then Q1 is indeed in the OFF state.To calculate the stable state currents and voltages consider a practical circuit.

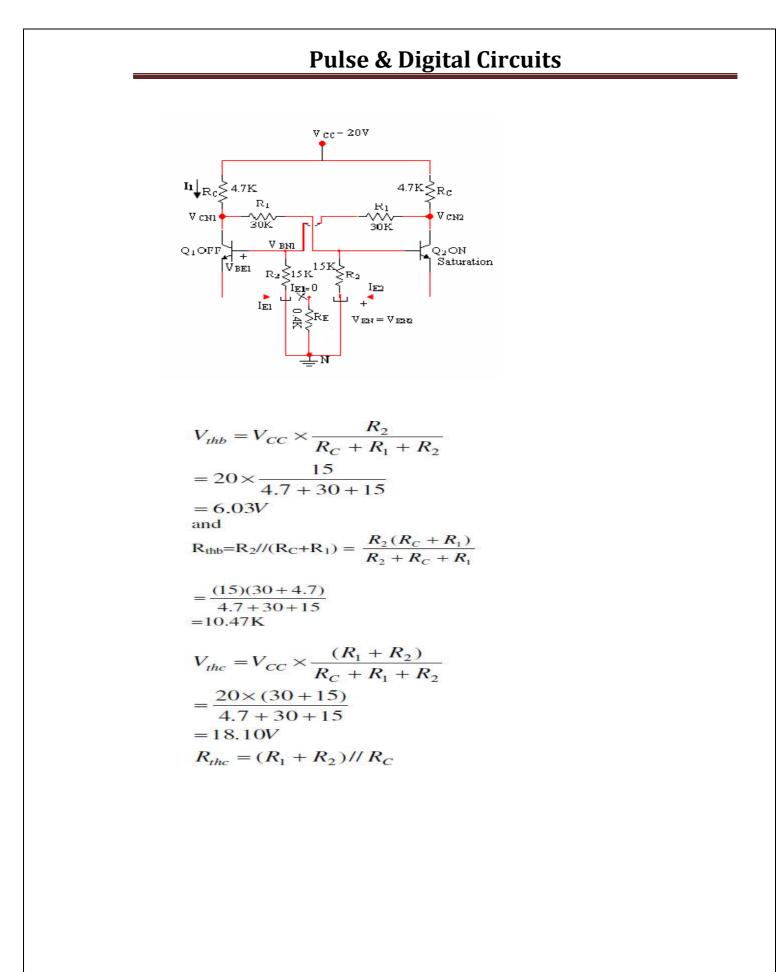

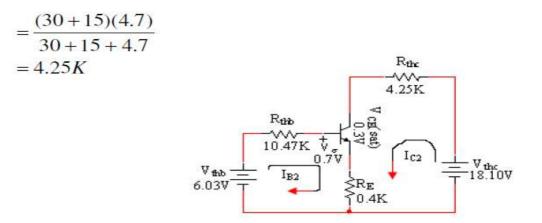

In npn silicon transistors are used.  $V_{BE(sat)} = 0.7V$ ,  $V_{CE(sat)} = 0.4V$  and  $h_{FEmin} = 50$ ,

$V_{CC} = 20V, R_C = 6.7K, R1 = 30K \text{ and } R2 = 15K, R_E = 400\Omega$

Let Q1 be OFF and Q2 be ON. As Q1 is OFF,  $I_{E1} = 0$ . To verify whether Q2 is in Saturation or not , draw the collector loop and base loop of the circuit by the venising at the collector and base terminals.

### **Pulse & Digital Circuits**

Using KVL at the input and output loops

$6.03-0.7 = (10.47+0.4) I_{B2}+0.4I_{C2} \quad \dots \quad (1)$  $18.10-0.3 = 0.4I_{B2} + (6.25+0.4) I_{C2}$  ----- (2) i.e.  $5.33V = 10.87I_{B2} + 0.4I_{C2}$ 17.80V=0.4I<sub>B2</sub>+6.65I<sub>C2</sub> From which a. IB2=0.35mA Ic2=3.79mA  $I_{B2\min} = \frac{I_{C2}}{h_{FF}} = \frac{3.79mA}{50}$ = 0.076 mA $I_{B2} >> I_{B2\min}$ Hence Q<sub>2</sub> is saturation  $\therefore V_{EN} = V_{EN2} = (I_{B2} + I_{C2})R_E$  $V_{CN2} = V_{EN2} + V_{CE(sat)}$ =(1.66V + 0.4V) = 2.06V $V_{BN2} = V_{EN2} + V_{\sigma}$ =(1.66V+0.7V)=2.36V $V_{BN1} = V_{CN2} \times \frac{R_2}{R_1 + R_2}$  $=\frac{2.06 \times 15}{100}$ 15 + 30= 0.69V $V_{BE1} = V_{BN1} - V_{EN2}$ =(0.69V - 1.66) = -0.97V

As this voltage reverse biases the emitter diode, Q<sub>1</sub> is OFF.

www.FirstRanker.com

# **Pulse & Digital Circuits**

$$I_{1} = \frac{V_{CC} - V_{BN2}}{R_{C} + R_{1}}$$

=  $\frac{20 - 2.36}{4.7 + 30}$

=  $0.51mA$

$V_{CN1} = V_{CC} - I_{1}R_{C}$

=  $20 - (0.51)(4.7)$

=  $17.6V$

The stable state voltages are

$V_{CN1} = 17.6V$ ,  $V_{BN1} = 0.69V$

$V_{CN2} = 2.06V$ ,  $V_{BN2} = 2.36V$

$V_{EN} = 1.66V$

### 3.7 Schmitt trigger:

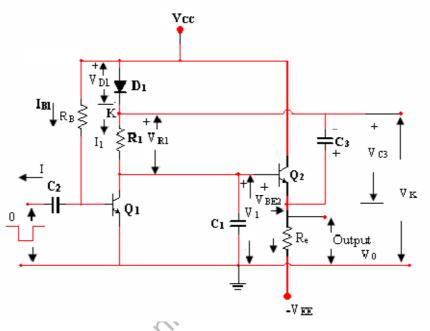

:Ranker.com It is an emitter coupled binary it is also called inventor. The following circuit represents Schmitt trigger.

# **Pulse & Digital Circuits**

#### Fig 1 .schmitt trigger

Schmitt trigger belongs to a class of bistable multivibrator circuits. In a bistable, there exist two D.C. couplings from each output to input of the other. But in Schmitt trigger circuit, there exists only one coupling. It can be recalled that if in the emitter coupled bistable the feedback network from the collector of transistor  $Q_2$  to the base of transistor  $Q_1$  is removed, it becomes a Schmitt trigger circuit.

The Schmitt trigger is used for wave shaping circuits. It can be used for generation of a square wave from a sine wave input. Basically, the circuit has two opposite operating states like in all other multivibrator circuits. However, the trigger signal is not, typically, a pulse waveform but a slowly varying A.C. Voltage. The Schmitt trigger is level sensitive and switches the output state at two distinct trigger levels. One of the triggering levels is called a lower trigger level (abbreviated as L.T.L) and the other as upper trigger level (abbreviated as U.T.L).

Above Figure1 shows the circuit of a Schmitt trigger, the circuit of Schmitt trigger contains of two identical transistors  $Q_1$  and  $Q_2$  coupled through an emitter  $R_E$ . The <u>resistors</u>  $R_1$  and  $R_2$  form a voltage divider across the  $V_{CC}$  supply and ground. These resistors provide a small forward bias on the base of transistor  $Q_2$ .

Let us suppose that initially there is no signal at the input. Then as soon as the power supply  $V_{CC}$  is switched on, the transistor  $Q_2$  starts conducting. The flow of its current through resistor  $R_E$  produces a voltage drop across it. This voltage drop acts as a reverse bias across the emitter junction of transistor  $Q_1$  due to which it cuts-off. As a result of this, the voltage at its collector rises to  $V_{CC}$ . This rising voltage is coupled to the base of transistor  $Q_2$  through the resistor  $R_1$ . It increases the forward bias at the base of transistor  $Q_2$  and therefore drives it into saturation and holds it there. At this instant, the collector voltage, level are  $V_{C1} = V_{CC}$  and  $V_{C2} = V_{CE(sat)}$  as shown in Figure 2.

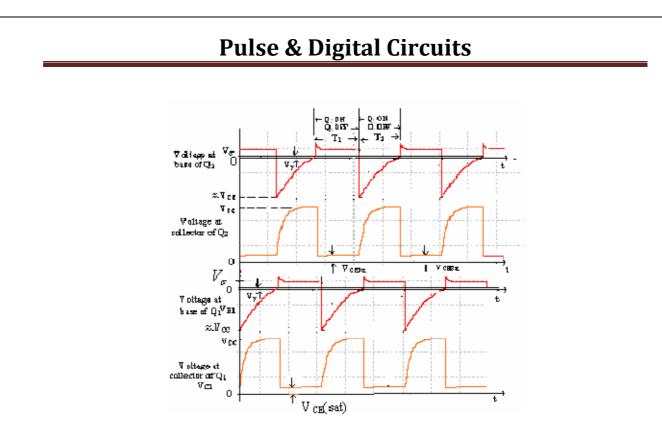

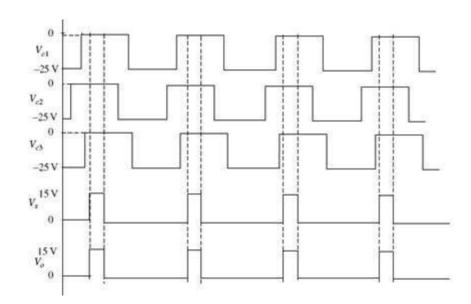

Figure 2: Waveforms at the input and collector of transistor Q1 and Q2

suppose an A.C. signal is applied at the input of the Schmitt trigger (i.e. at the base of the transistor Q<sub>1</sub>). As the input voltage increases above zero, nothing will happen till it crosses the upper trigger level (U.L.T). As the input voltage increases, above the upper trigger level, the transistor Q<sub>1</sub> conducts. The point, at which it starts conducting, is known as upper trigger point (U.T.P). As the transistor Q<sub>1</sub> conducts, its collector voltage falls below V<sub>CC</sub>. This fall is coupled through resistor R<sub>1</sub> to the base of transistor Q<sub>2</sub> which reduces its forward bias. This in turn reduces the current of transistor Q<sub>2</sub> and hence the voltage drop across the resistor R<sub>E</sub>. As a result of this, the reverse bias of transistor Q<sub>1</sub> is reduced and it conducts more. As the transistor Q<sub>1</sub> conducts more heavily, its collector further reduces due to which the transistor Q<sub>1</sub> conducts near cut-off. This process continues till the transistor Q<sub>1</sub> is driven into saturation and Q<sub>2</sub> into cut-off. At this instant, the collector voltage levels are V<sub>C1</sub> = V<sub>CE(sat)</sub> and V<sub>C2</sub> = V<sub>CC</sub> as shown in the figure.

# **Pulse & Digital Circuits**

The transistor  $Q_1$  will continue to conduct till the input voltage falls below the lower trigger level (L.T.L). It will be interesting to know that when the input voltage becomes equal to the lower trigger level, the emitter base junction of transistor  $Q_1$  becomes reverse biased. As a result of this, its collector voltage starts rising toward  $V_{CC}$ . This rising voltage increases the forward bias across transistor  $Q_2$  due to which it conducts. The point, at which transistor  $Q_2$  starts conducting, is called lower trigger point (L.T.P). Soon the transistor  $Q_2$  is driven into saturation and  $Q_1$  to cur-off. This completes one cycle. The collector voltage levels at this instant are  $V_{C1} = V_{CC}$  and  $V_{C2} = V_{CE(sat)}$ . No change in state will occur during the negative half cycle of the input voltage.

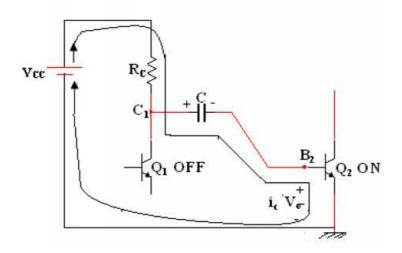

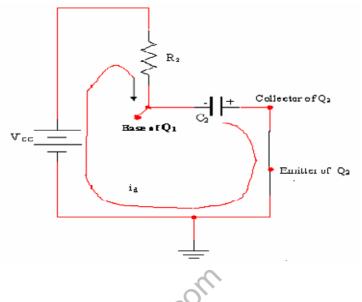

### 3.8 Monostable Multivibrator

### Introduction:

This circuit consists of two active devices Q1 and Q2, one is in the OFF state, say (Q1) and the other, Q2 in the ON state. These devices remain in the same state forever. Only on the application of a trigger, the multi goes into the quasi stable state (Q1 ON and Q2 OFF) and after a time interval T, will return to the stable state (Q1 OFF and Q2 ON). Thus this circuit generates a gate pulse of duration Tether output of this circuit is high for a time duration T called the pulse duration, pulse width or gate width.

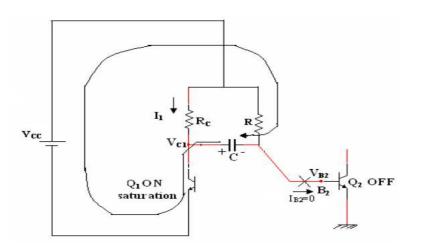

### **Collector-Coupled monostable multivibrator:**

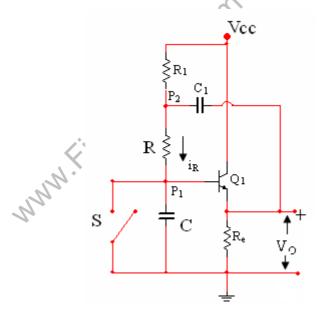

The collector coupled monostable multivibratoris shown below.

www.FirstRanker.com

# **Pulse & Digital Circuits**

Fig. Collector-coupled monostable multivibrator.

Ranker.com In the stable state Q1 is OFF and Q2 is ON . Therefore

$V_{C1} = V_{CC}$

$V_{B2} = V_{CE(sat)}$

### **Pulse & Digital Circuits**

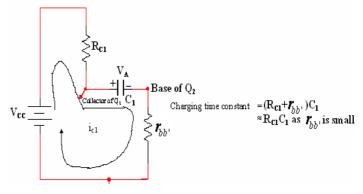

#### **Fig. Charging of C**

C now tries to charge to  $V_{CC}$  through  $R_C$  of Q1 and small input resistance of Q2.As  $t \rightarrow \infty$ , this voltage reaches  $V_{CC}$ . On the application of a trigger at t=0, (a negative pulse at B2), Q2 goes into the OFF state and Q1 is driven into the ON state and preferably into saturation. Hence there is a current I<sub>1</sub> in Q1.  $V_{C1}$  is  $V_{CF(sat)}$ , if I<sub>1</sub>=I<sub>C(sat)</sub>.

Fig. discharging of c

# **Pulse & Digital Circuits**

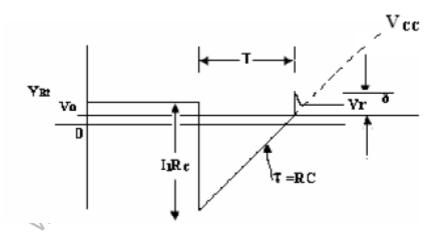

The charge on C now discharges with a time constant  $\tau$ =RC,. As a result the voltage at B<sub>2</sub> changes as a function of time .When this voltage V<sub>B2</sub> at B<sub>2</sub> reaches V<sub>γ</sub> after a time interval T, Q2 is switched ON and Q1 is switched OFF due to regeneration, thus ending the quasi stable state.

The voltage variation at  $B_2$  of Q2

Fig. Voltage variation at the base of Q2 in the quasi stable state.

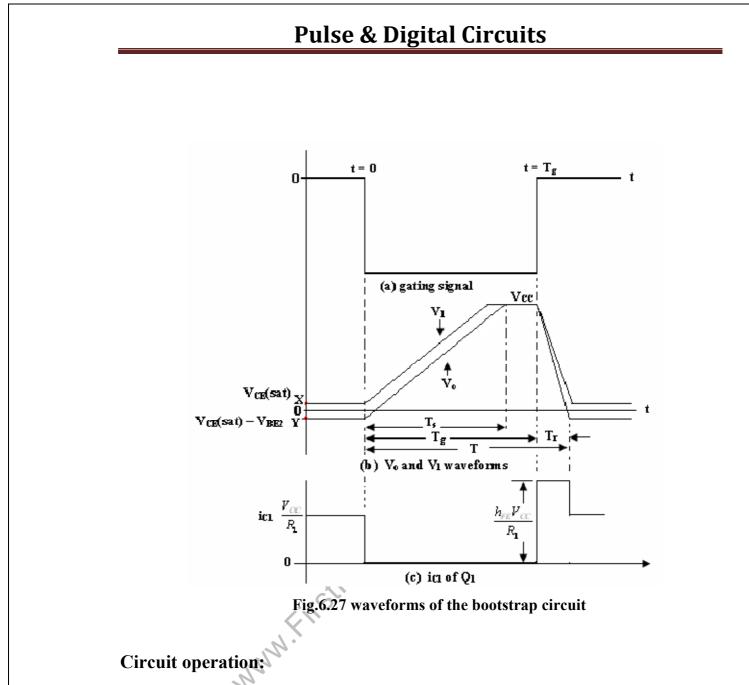

The time period T can be calculated as T= 0.69RC, if Q1 in the quasi stable state is in saturation, since  $I_1RC = V_{CC}-V_{CE(sat)}$

### Gate width of a collector coupled mono stable:

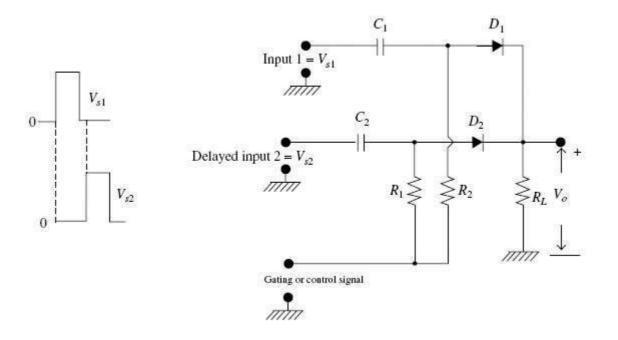

A mono stable multi can be used as a voltage to time converter as shown in Fig

www.FirstRanker.com

### Fig. . Monostable as a voltage to time converter

The time T for which Q1, in the quasi stable state, is ON and Q2 is OFF is calculated. Consider the voltage variations at B2, fig.7.17

www.FirstRanker.com

www.FirstRanker.com

# **Pulse & Digital Circuits**

$$V_{B2}(t) = V_f - (V_f - V_i)e^{\frac{-t}{\tau}}$$

$$V_f = V$$

$$V_i = V_{\sigma} - I_1 R_C$$

If Q<sub>1</sub> is in saturation

$$I_1 R_C = V_{CC} - V_{CE}(sat)$$

$$V_i = V_{\sigma} - V_{CC} + V_{CE}(sat)$$

$$V_{B2}(t) = V - (V - V_{\sigma} + V_{CC} - V_{CE}(sat))e^{\frac{-\tau}{\tau}}$$

At  $t = T$

$V_{B2}(t) = V_{\gamma}$

$V_{\gamma} = V - (V - V_{\sigma} + V_{CC} - V_{CE}(sat)e^{\frac{-T}{\tau}}$

As  $V_{\gamma}$ ,  $V_{\sigma}$  and  $V_{CE}(sat)$  are small when compared to V and  $V_{CC}$

$\therefore 0 = V - (V + V_{CC})e^{\frac{-T}{\tau}}$

$T = \tau \ln \frac{(V + V_{CC})}{V}$

$T = \tau \ln (1 + \frac{V_{CC}}{V})$

Thus, to change T, V can be varied.

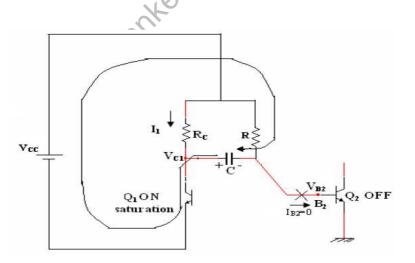

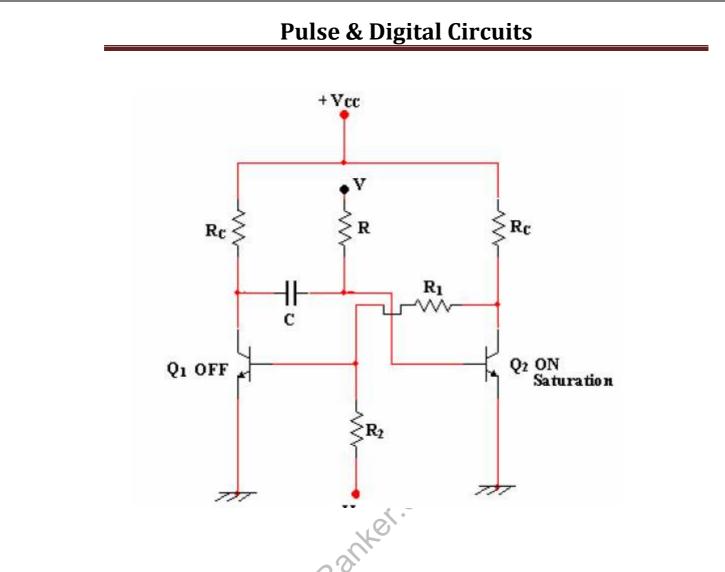

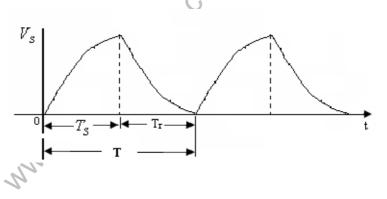

3.9 Astable multivibrator

### Introduction:

Two cross-coupled switching circuits are connected in this arrangement. The devices in this Multivibrator will not remain in one state (either ON or OFF) forever. Change of state in the devices occurs continuously after a finite time interval depending on the circuit components used. Hence this circuit has two quasi stable states.

Let Q1 and Q2 be two transistors used. If Q1 is ON, then Q2 is OFF. These will remain in this state only for a fixed time duration after which Q1 switches into the OFF state and Q2 into the ON state without applying triggering pulse and this process is repeated. Therefore it

# **Pulse & Digital Circuits**

is also called Free running multivibrator. The output of the circuit is a squarewave, having two time periods, T1 and T2. If T1 = T2=T/2, then the circuit is a symmetric astable multivibrator. If T1 $\neq$ T2, then it is called an unsymmetrical astable multi-vibrator. The astable multivibrator is essentially a square wave generator

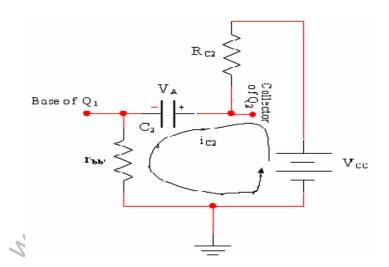

#### **Collector Coupled astable multi:**

Collector coupled astable multi is shown below.

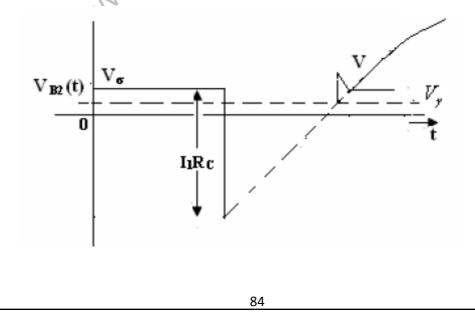

Fig. astable multi vibrator

Assume that transistor Q1 is OFF and Q2 is ON initially. Then  $V_{B2} = V_{\sigma}$ ,  $V_{C2} = V_{CE(sat)}$  and  $V_{C1}=V_{CC}$ . With Q1 OFF and Q2 ON, C1 will try to charge to the supply voltage through the collector resistance  $R_{C1}$  and through the base and emitter terminals of Q2.

# **Pulse & Digital Circuits**

Fig. Charging of capacitor C1

Prior to this condition, Q2 must have been in the OFF state and Q1 must have been in the ON state. As a result C2 must have been charged through  $R_{C2}$ . Between the base and emitter terminals of Q1,

Fig.charging of capacitor C2

When Q2 suddenly changes from the OFF state to ON state, the voltage between its collector and emitter terminals is  $V_{CE}$ . Hence the collector of Q2 is at ground potential i.e. the positive end of the capacitor C2 is at the ground potential and its negative terminal is connected to base of Q1. As a large negative voltage is now coupled to base ofQ1, Q1 is indeed in the OFF state.

# **Pulse & Digital Circuits**

But Q1 is not going to remain in the OFF state forever. Now, with Q2 ON, the charge on the capacitor C2 discharges with a time constant  $\tau_2 = R2C2$ .

Fig. discharge of C2 through R2

As a result, the voltage at the base of Q1 goes on changing as a function of time .Once this voltage is  $V_{\gamma}$ , Q1 draws base current. Hence there is a collector current; there is a voltage drop across  $R_{C1}$  and the voltage at the collector of Q1 falls. Earlier this voltage was  $V_{CC}$  and now it is smaller than  $V_{CC}$ . Therefore, the negative step at this collector is coupled to the base of Q2 through  $C_1$ . As the collector of Q1 and the base of Q2 are connected through  $C_1$  and as a capacitor will not allow any sudden changes in voltage, whatever is the change that has taken place at the first collector an identical change takes place at the base of Q2. As a result the base current of Q2 is reduced, its collector current is reduced and the voltage at its collector rises. This positive step change is coupled to the base of Q1. Its base current further increases. The collector current increases, the voltage at the collector of Q1 further falls and this change is coupled to the base Q2 and this process is repeated. Thus a regenerative action takes place and Q2 switches into the OFF state and Q1 goes into the ON state. The waveforms at the base and collectors of Q1 and Q2 are shown below.

#### Fig. Waveforms of collector-coupled astable multi

When suddenly the transistor changes from the OFF state to the ON state there could be a small overshoot at this base and at the collector of the other transistor. Further, it is seen that when a transistor changes from the ON state into OFF state, say Q1, its collector voltage is required to abruptly rise to  $V_{CC}$ . But when Q1 is OFF and Q2 is ON, there is a charging current of capacitor C1. As a result the voltage  $V_{C1}$  will not suddenly rise to  $V_{CC}$ . Only when this charging current is zero, the collector voltage reaches  $V_{CC}$ . Hence, there is rounding off of the rising edge of the pulse.

### **Important Questions:**

- 1. What is a multivibrator? what are the types of it?

- 2. What are types of triggering?

- 3. What is the resolution time ? how it can be improved?

- 4. Explain operation of bistable multivibrator? calculate pulse width?

- 5.Explain operation of Monostable multivibrator? calculate pulse width?

- 6. Explain operation of astable multivibrator? calculate pulse width?

- 7. Explain operation of Schmitt trigger?

# **Pulse & Digital Circuits**

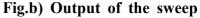

### <u>UNIT-V</u> <u>TimeBase Generators</u>

### 4.1 Voltage Sweep Generators

### Introduction:

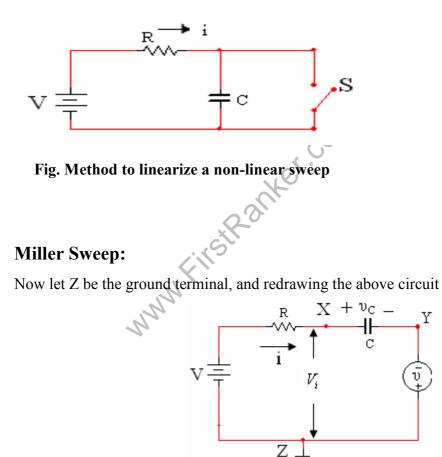

A linear time-base generator is one that provides an output waveform a portion of which Exhibits a linear variation of voltage or current with time. Earlier, this waveform is used to sweep the electron beam horizontally across the screen. Because of this reason it is called **sweep voltage**.

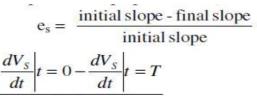

### 4.2 Errors that define deviation from linearity

Quality of a sweep is specified by three errors that define deviation from linearity.

Errors that define deviation from linearity are three types.

i)The slope error or speed error  $e_s$

ii)Displacement error  $e_d$

iii)Transmission error  $e_t$

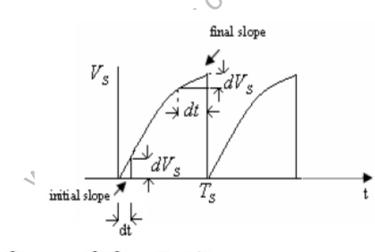

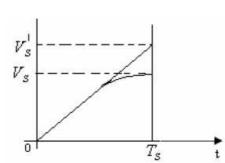

### (a)Slope or sweep speed error ,es

# $\frac{dV_s}{dt}t = 0$

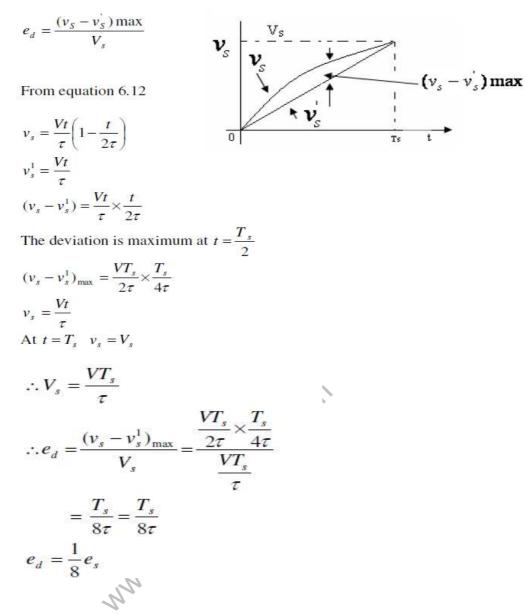

(b) Displacement error, e<sub>d</sub> :

### **Pulse & Digital Circuits**

It is the maximum difference between the actual sweep voltage and the linear sweep which posses through the beginning and end points of the a sweep.

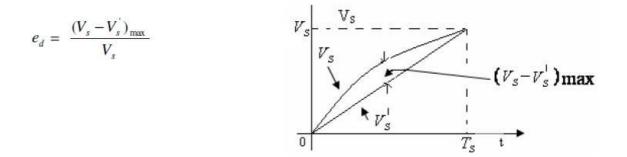

### (c)Transmission error, e<sub>t</sub>:

If a ramp voltage is transmitted through a highpass RC circuit, the output falls away from the input.

$$e_t = \frac{(V_s' - V_s)}{V_s'}$$

$V_s$  is the actual output  $V_s$  is the input

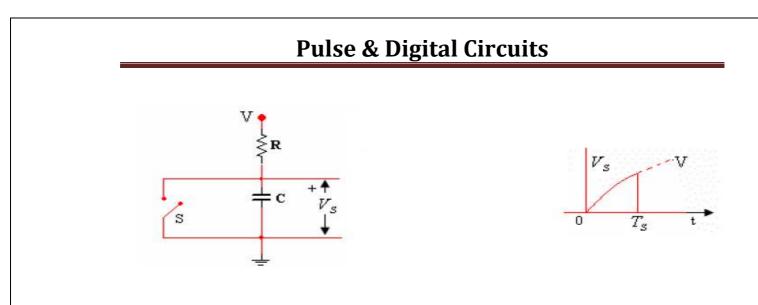

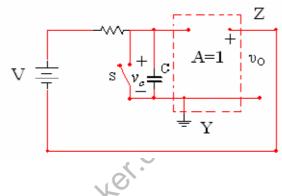

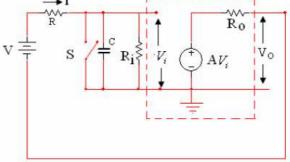

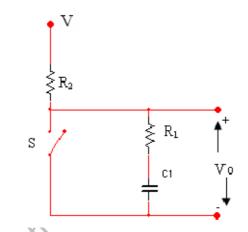

### 4.3 Exponential sweep generator:

A simple exponential sweep generator and its output are shown in Figs. a) and b) respectively If initially the capacitor is uncharged and t = 0 the switch S is open, the capacitor charges to the supply voltage V.

# Fig.a) A simple exponential sweep generator generator

If the resistance offered by the switch is ideally not zero there is a finite time delay before the signal reaches its initial value. This time delay is called fly back time, restoration time or retrace tie.

Normally  $Tr \ll Ts$ , so T=Ts

#### Fig. output waveform of exponential sweep

The voltage variation in the capacitor C is

$$v_{c}(t) = V_{f} - (V_{f} - V_{i})e^{-t/\tau}$$

=  $V - (V - 0)e^{-t/\tau}$

$v_{c}(t) = v_{s} = V(1 - e^{-t/\tau})$

### **Pulse & Digital Circuits**

Assume that after an interval Ts when s v = Vs, the switch closes. The charge on the capacitor discharges with a negligible time constant and the voltage abruptly falls to zero at t = TS.

| $v_s = V(1 - e^{-t/\tau})$                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------|

| $\frac{dv_s}{dt} = -Ve^{-t/\tau} \left(-\frac{1}{\tau}\right) = \frac{V}{\tau}e^{-t/\tau}$                                              |

| $\frac{dv_s}{dt} t = 0 = \frac{V}{\tau}$                                                                                                |

| $\frac{dv_s}{dt} t = T_s \qquad =  \frac{V}{\tau} e^{\frac{-T_s}{\tau}}$                                                                |

| $\therefore e_s = \frac{\frac{V}{\tau} - \frac{V}{\tau}e^{\frac{-T_s}{\tau}}}{\frac{V}{\tau}} = \left[1 - e^{\frac{-T_s}{\tau}}\right]$ |

| at $t = T_s, v_s = V_s$                                                                                                                 |

at  $t = T_s, v_s = V_s$

Hence

$$V_s = V\left(1 - e^{\frac{-T_s}{\tau}}\right)$$

$$\therefore 1 - e^{-T_s/\tau} = \frac{V_s}{V}$$

Substituting ,we have

$$e_s = \frac{V_s}{V}$$

From above equation it is evident that s e is small when  $V >> V_s$ . i.e. the linearity improves if V is large when compared to s V. Therefore, a simple exponential sweep suffers from the disadvantage that a linear sweep is generated only when the sweep amplitude is very much small when compared to the applied d.c. voltage, V

If

www.FirstRanker.com

# **Pulse & Digital Circuits**

$$\frac{t}{\tau} \ll 1$$

$$e^{-t/\tau} = 1 - \frac{t}{\tau} + \frac{t^2}{2\tau^2} - \frac{t^3}{6\tau^3} + \Lambda$$

$$v_s = V\left(1 - e^{-t/\tau}\right)$$

$$= V\left[1 - 1 + \frac{t}{\tau} - \frac{t^2}{2\tau^2} + \frac{t^3}{6\tau^3}\Lambda\right]$$

$$= \frac{Vt}{\tau}\left[1 - \frac{t}{2\tau} + \frac{t^2}{6\tau^2}\right]$$

Since  $v = V_s$  at  $t = T_s$

To first approximation

As this is a linear sweep

$V_s = \frac{VT_s}{\tau}$

Hence, for  $e_s$  to be small  $\tau >> T_S$

If the actual sweep is non-linear, consider the first two terms

$$v_s = \frac{Vt}{\tau} \left( 1 - \frac{t}{2\tau} \right)$$

$$\therefore V_s = \frac{VT_s}{\tau} \left( 1 - \frac{T_s}{2\tau} \right)$$

This is a non-linear sweep

Therefore the transmission error  $e_t$  is

www.FirstRanker.com

# **Pulse & Digital Circuits**

$$e_t = \frac{T_s}{2\tau} = \frac{e_s}{2\tau}$$

# **Pulse & Digital Circuits**

The interrelationship between the three types of errors is given below

$$e_d = \frac{1}{8}e_s = \frac{1}{4}e_t$$

If we know one type of error, we can calculate the other types of errors

$$C = \frac{I}{C}t.$$

If the capacitor is charged with a constant current I then the voltage across *t*.hence, the rate of change of voltage with time is called sweep speed.

# **Pulse & Digital Circuits**

Sweep speed

$$=\frac{I}{C}$$

### 4.4 UJT sweep generator:

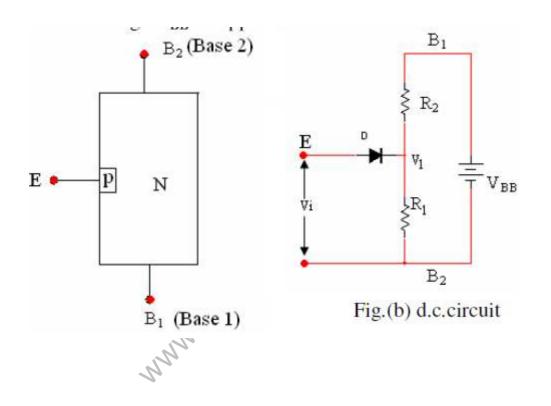

In the exponential sweep generator, a UJT can be used as switch S. The UJT and its d.c circuit are shown in figs. below. A UJT consists of an N-type semiconductor bar with leads  $B_1$  and  $B_2$  drawn. Emitter is a P-type material and it is heavily doped. Let the bias voltage  $V_{BB}$  be applied.

We have,

$$V_1 = V_{BB} \frac{R_1}{R_1 + R_2}$$

=  $V_{BB} \frac{R_1}{R_{BB}} = \eta V_{BB}$

# **Pulse & Digital Circuits**

Where  $\eta$  = Intrinsic stand-of-ratio (lies around 0.7)

As long as  $V_i \ll \eta V_{BB}$  D is OFF.

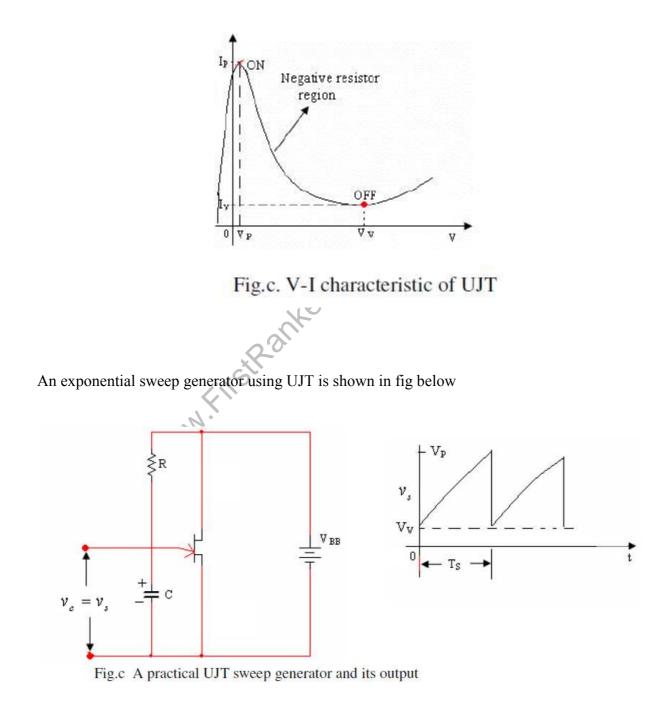

When  $V_i > \eta V_{BB}$  D is ON and a large number of charge carriers exist on the N-side, reducing the resistance and the device conducts heavily, switch S is closed. The V-I characteristic of a UJT is shown in fig.c

www.FirstRanker.com

# **Pulse & Digital Circuits**

$$v_{s} = V_{BB} \left( 1 - e^{-t/\tau} \right)$$

At  $t = T_{s}, v_{s} = \eta V_{BB}$

$\eta V_{BB} = V_{BB} \left( 1 - e^{-t/\tau} \right)$

$V_{BB} e^{-T_{s}/\tau} = V_{BB} (1 - n)$

$$V_{BB}e^{-T_s/\tau} = V_{BB}(1-n)$$

$$T_s = \tau \ln \frac{1}{(1-n)}$$

### Alternately

$$v_{s} = V_{f} - (V_{f} - V_{i})e^{-t/\tau}$$

$$= V_{BB} - (V_{BB} - V_{v})e^{-t/\tau}$$

At  $t = T_{s}, v_{s} = V_{s} = V_{p}$

$$V_{p} = V_{BB} - (V_{BB} - V_{v})e^{-T_{s}/\tau}$$

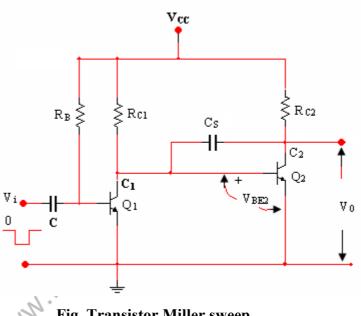

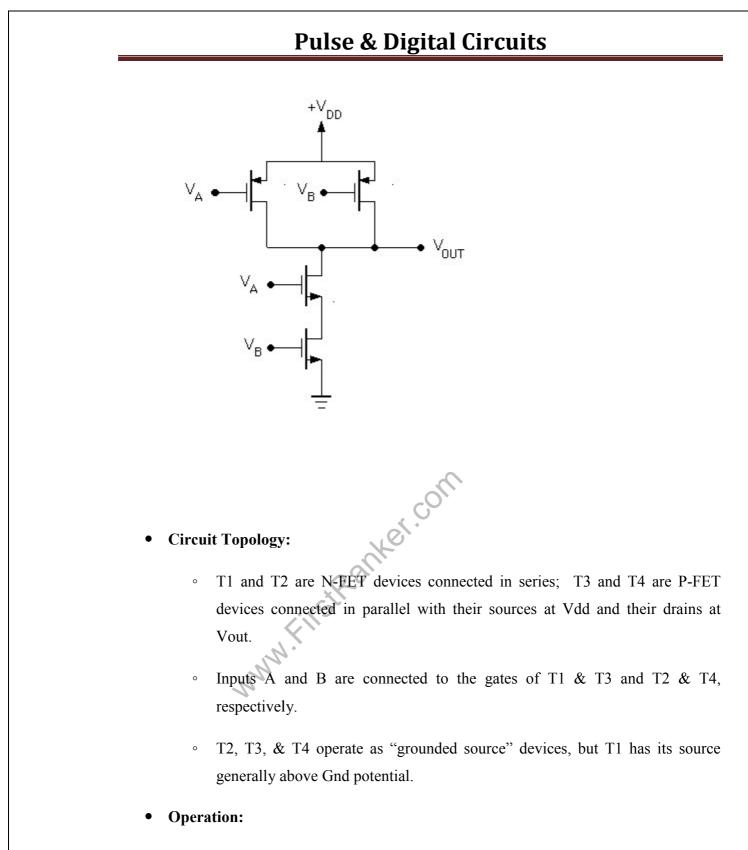

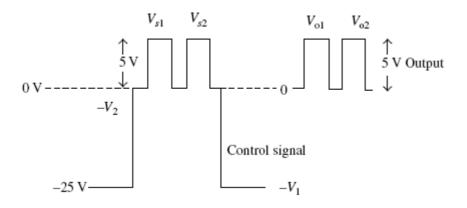

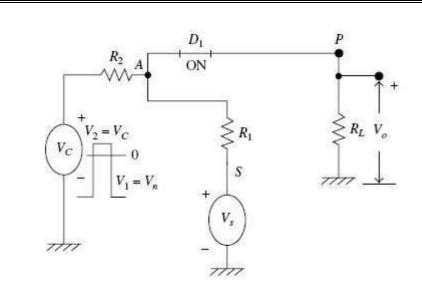

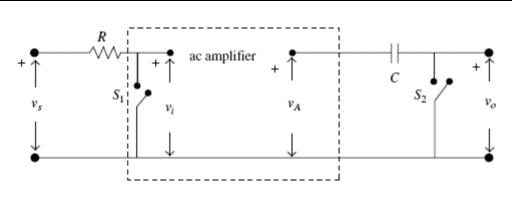

$$T_{s} = \tau \ln \frac{(V_{BB} - V_{v})}{(V_{BB} - V_{p})}$$