www.FirstRanker.com

**R16**

#### Code No: 134CC JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY HYDERABAD B.Tech II Year II Semester Examinations, May - 2019 PULSE AND DIGITAL CIRCUITS (Common to ECE, ETM)

# Time: 3 Hours

FirstRanker.com

Note: This question paper contains two parts A and B. Part A is compulsory which carries 25 marks. Answer all questions in Part A. Part B consists of 5 Units. Answer any one full question from each unit. Each question carries 10 marks and may have a, b, c as sub questions.

### PART-A

- 1.a) Show how an RC circuit works as a high pass filter.

- b) Illustrate the output voltage and loop current waveform of a RC low pass circuit for a step input and indicate the time constant. [3]

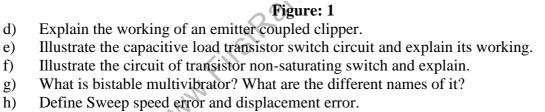

- c) The input to the clipper circuit is  $V_m Sin\omega t$ . Illustrate the input and output waveform with respect to transfer characteristics shown in figure 1. [2]

D1

- i) Illustrate the diode OR circuit for negative logic and give its truth table.

- j) What is sampling gate? How it is different from logic gate?

#### PART-B

(50 Marks)2. A symmetrical square wave whose average value is zero has a peak to peak amplitude of 20V and a period of 2µsec. This waveform is applied to a low-pass RC circuit whose 3dB frequency is  $1/2\pi$  MHz. Determine and sketch the steady state output waveform. In particular, what is the peak-to-peak output amplitude? [10]

#### OR

3. A square wave whose peak-to-peak amplitude is 2V extends  $\pm 1V$  wrt ground. The duration of the positive section is 0.1 sec and that of the negative section is 0.2 sec. If this waveform is impressed upon an RC integrating circuit whose time constant is 0.2 sec, Evaluate the steady state maximum and minimum values of the output waveform. [10]

Max. Marks: 75

# (**25 marks**) [2]

[3]

[2]

[3]

[2]

[3]

[2]

[3]

www.FirstRanker.com

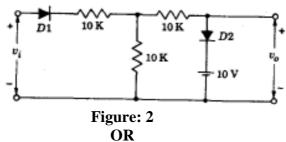

- 4. The diodes are ideal.

- a) Write the transfer characteristic equation.

- b) Plot  $v_o$  against  $v_i$  indicating all intercepts, slopes and voltages.

- c) Determine and sketch  $v_o$  if  $v_i = 40 \sin \omega t$ . Indicate all voltage levels. (Figure 6) [10]

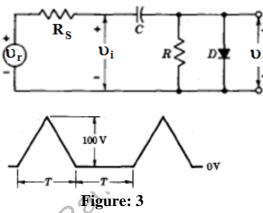

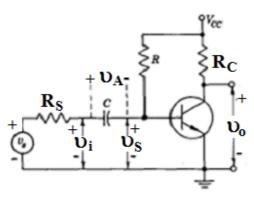

5. The ramp type signal is applied to the circuit shown in figure 3 which has  $R_f=100\Omega$ ,  $V_r=0$ ,  $R_r=\infty$  and  $R=10K\Omega$ . The capacitor C is arbitrarily large. Develop the output waveform, calculate all voltage levels and voltage across the capacitor, if  $R_s=0$  and  $100\Omega$ .

[10]

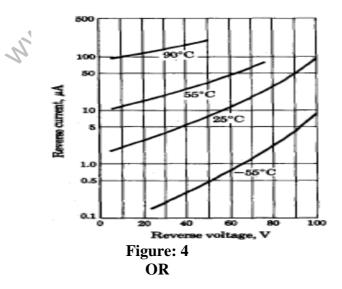

6. A reverse biasing voltage of 100V is applied through a resistor R to a type of diode 1N270 diode. The diode operates at  $25^{0}$ C. Determine the diode current and voltage for the cases R=10M $\Omega$ , 1M $\Omega$  and 100K $\Omega$ .(Figure 4) [10]

www.FirstRanker.com

irstRanker.<mark>com</mark>

7. In the below circuit  $V_{CC}=10V$ ,  $R_C=500\Omega$ ,  $R=40K \Omega$ ,  $C=0.1\mu$ F,  $R_{s1}=R_{s2}=10K \Omega$ , V=10V and  $T_2=1.0$ msec. Determine the all the marked voltages assuming rbb'=100  $\Omega$ .(Figure 5) [10]

Figure: 5

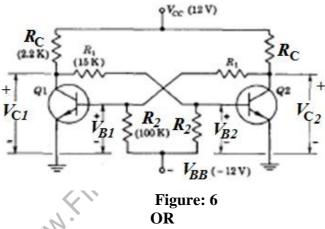

8. The fixed bias binary shown below figure 6 uses npn silicon transistors with  $h_{FE}=20$ . The circuit parameters are  $V_{CC}=12V$ ,  $V_{BB}=3V$ ,  $R_{C}=1K$ ,  $R_{1}=5K\Omega$  and  $R_{2}=10K\Omega$ . Test that one transistor is in cut-off and the other is in saturation and evaluate the stable state current and voltages if  $V_{CE(sat)}=0.4V$  and  $V_{BE(sat)}=0.8V$ . [10]

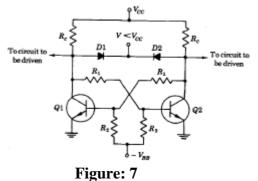

9. Germanium transistors with  $(h_{FE})_{min}=40$  are used in the fixed bias flip-flop with collector catching diodes. The circuit parameters are  $V_{CC}=18V$ ,  $V=V_{BB}=6V$ ,  $R_{C}=1.5K\Omega$ ,  $R_{i}=5K\Omega$  and  $R_{2}=25K\Omega$ . Neglect the voltage drop across a forward biased junction. Verify that if one transistor is cut-off, the other is in saturation. (Figure 7) [10]

FirstRanker.com

www.FirstRanker.com

- 10.a) Explain unidirectional sampling gate.

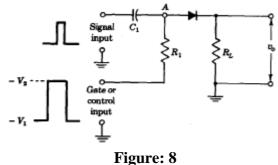

- b) In the gate circuit shown below figure 8,  $R_L=10K\Omega$  and is shunted by a capacitance  $C_1=10pF$ . The gate signal is a symmetrical square wave of frequency 1MHZ which makes excursions between -35 to 0V. The output impedance of the square wave source is 500 $\Omega$ . If no more than 2V of the input signal is to be fed back into the control-signal source, what is  $R_1$ ? [5+5]

## OR

- 11.a) Design the circuit of three input positive NAND gate and explain.

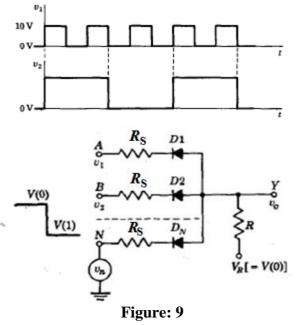

- b) Consider a two input positive-logic diode OR gate with the diodes reversed and  $V_r=0$ . The inputs are the square waves  $v_1$  and  $v_2$  indicated. Determine and sketch the output waveform if the ratio of the amplitude of  $v_1$  and  $v_2$  is: i) 2 ii) 0.5. Assume ideal diodes. (Figure9) [5+5]

---00000----