### Code No: G6806/R13

# M. Tech. I Semester Supplementary Examinations, January-2017

### **DIGITAL SYSTEM DESIGN**

(Common to VLSI & ES, ES & VLSI, VLSID & ES, ES & VLSID, VLSI, VLSID, VLSI&ME, ES, DE&CS, E&CE and DECE)

Time: 3 hours Max. Marks: 60

## Answer any FIVE Questions All Questions Carry Equal Marks

- 1. a List out the cube based operations that can be used in cube based minimization 6M algorithm and explain them with an example each.

- b Apply CAMP algorithm to minimize the given 4 variable Boolean function  $f(a, b, c, d) = \sum m(1, 3, 5, 7, 9, 10, 13, 14, 15)$

- - b List out the steps to be consider for PLA folding algorithm?

- 3. a Design a combinational circuit using a ROM. The circuit accepts a 3 bit number and generates an output binary number equal to the square of the input number.

- b How a sequential circuit can be designed using FPGA? 4M

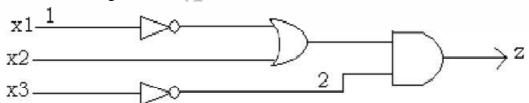

- 4. a Using the path-sensitization method and Boolean difference method find the test vectors for SA0 fault on input line 1 and SA1 fault on the internal line 2 of the circuit shown in figure

b Write a short note on Fault classes and Models?

1 of 2

#### www.FirstRanker.com

Code No: G6806/R13

| 5. a | Ps | Ns, z<br>x=0, x=1 | Conduct a Homing experiment and determine shortest homing sequence which identifies the final state of the given |

|------|----|-------------------|------------------------------------------------------------------------------------------------------------------|

|      | A  | B,0 D,0           | state machine.                                                                                                   |

|      | В  | A,0 B,0           |                                                                                                                  |

|      | C  | D,1 A,0           |                                                                                                                  |

|      | D  | D,1 C,0           |                                                                                                                  |

|      |    |                   |                                                                                                                  |

4M

8M

- b Explain the properties of a successor tree.

- 6. a Simplify the Boolean expression using k-map  $F = \pi M (0, 1, 3, 5, 6, 7, 10, 14, 15)$

6M

b Compare PROM, PLA and PAL.

6M

7. a Discuss the BIST scheme for PLD and CPLDs.

6M 6M

Classify the fault detection experiments for the sequential circuits with examples.

12M

8. Draw an ASM chart to design control logic of a binary multiplier. Realize the same using MUX, decoder and D-type flip flops. ANN FIRST PARTY